PVD (폴리프로필)

PVD는 대상 물질을 스퍼터링하거나 증발시켜 금속 증기를 생성한 다음 웨이퍼 표면에 금속 증기를 응축시키는 과정입니다. PVD 기술 개발 분야에서 25년 이상의 경험을 쌓아온 어플라이드 머티어리얼즈는 이 분야에서 명실상부한 시장 리더입니다.

PVD 증착 공정은 반도체 제조에서 다양한 로직 및 메모리 소자를 위한 초박형, 초고순도 금속 및 전이 금속 질화물 필름을 만드는 데 사용됩니다. 가장 일반적인 PVD 응용 분야는 알루미늄 플레이트 및 패드 금속화, 티타늄 및 티타늄 질화물 라이너, 배리어 층 증착 및 인터커넥트 금속화를 위한 구리 배리어 시드 증착입니다.

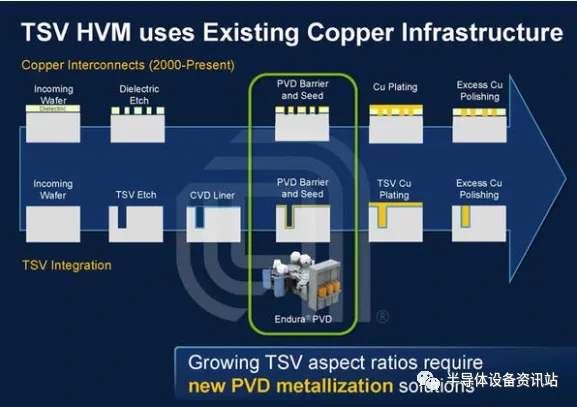

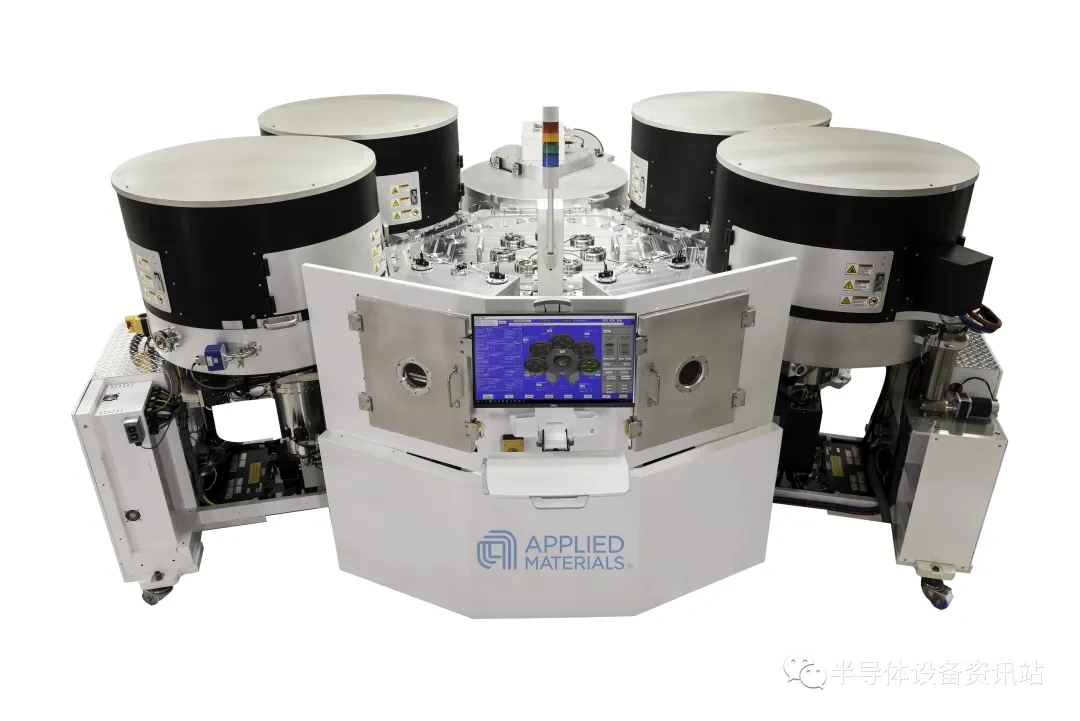

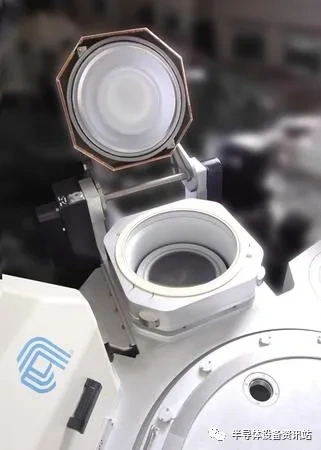

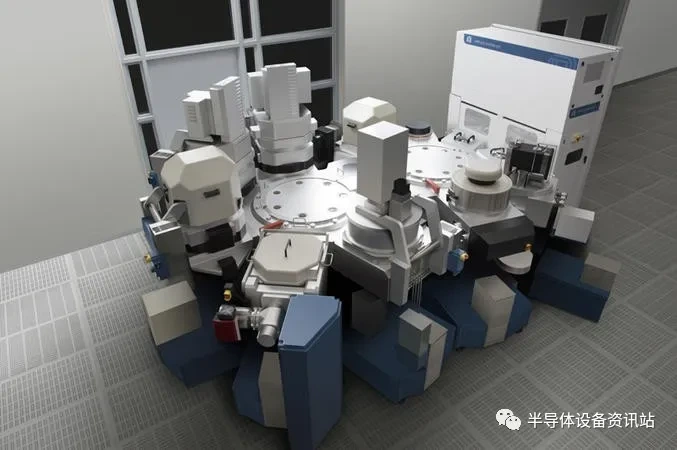

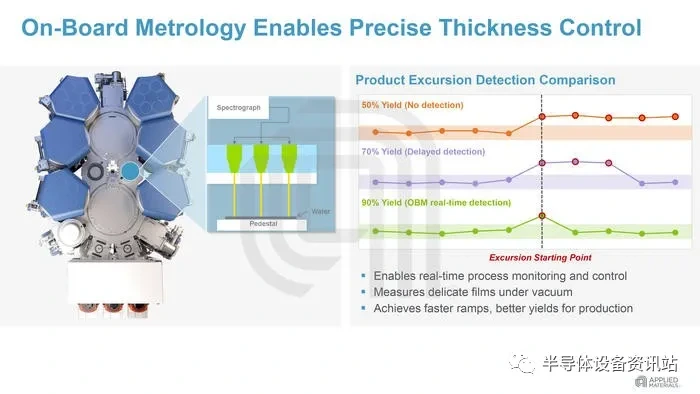

PVD 박막 증착 공정에는 최상의 계면과 박막 품질을 달성하기 위해 PVD 증착 공정이 탈기 및 표면 전처리 기술과 통합된 고진공 플랫폼이 필요합니다. 어플라이드의 Endura 플랫폼은 PVD 금속화를 위한 현재 업계 표준입니다.

엔듀라 PVD

오늘날 200mm 물리 기상 증착(PVD)의 과제는 더 두껍고 매우 균일하며 저온 호환 가능한 필름을 증착할 수 있다는 것입니다. 전력 장치 시장에서는 작은 폼 팩터와 공간 점유율로 고속으로 전환할 수 있는 장치가 4μm에서 100μm 이상에 이르는 두께의 Al 층과 같은 고급 열 기술에 대한 수요를 주도하고 있습니다.

미세 전자 기계 시스템(MEMS), CMOS 이미지 센서 및 실리콘 관통 전극(TSV)과 같은 패키징 기술의 새로운 응용 분야는 질화알루미늄(AlN), 인듐 주석 산화물(ITO), 알루미나(Al2O3) 및 게르마늄(Ge)과 같은 박막에서 PVD의 개발을 주도하고 있습니다.

엔듀라 PVD 200mm

어플라이드의 Endura 플랫폼은 반도체 업계에서 가장 성공적인 금속화 시스템입니다. 프론트 엔드 금속화(예: 코발트, 텅스텐, 알루미늄 및 구리 인터커넥트) 및 언더 범프 금속화와 같은 패키징 응용 분야에 걸친 증착 기능을 통해 지난 20년 동안 제조된 대부분의 마이크로칩은 현재 전 세계적으로 4,500개 이상 판매된 Endura 시스템에서 생산되었습니다.

엄격한 필름 두께 제어, 탁월한 바닥 커버리지 및 높은 정합성을 통해 광범위한 초순수 필름을 증착할 수 있는 Endura의 능력은 최첨단 장치 제조의 핵심입니다. 이 시스템은 최대 9개의 공정 챔버를 수용할 수 있으며, 혼합 및 매칭 챔버를 통해 통합된 다단계 공정 시퀀스를 생성할 수 있습니다. 고도로 구성 가능한 Endura 플랫폼은 순수 산화물을 제거하기 위한 2개의 사전 세척 챔버, 최대 6개의 PVD 챔버 및 2개의 MOCVD 챔버(옵션)를 지원하여 고객의 박막 증착 및 소자 성능 요구 사항을 충족할 수 있도록 합니다.

업그레이드

수천 대의 Endura가 사용 중이며 그 중 다수는 원래 구성으로 되어 있으므로 공정 성능과 장비 생산성을 향상시키는 데 사용할 수 있는 여러 가지 제품 개선 사항을 제공합니다. 예를 들어, 냉각 챔버의 용량 병목 현상은 챔버 A를 플로우 스루 챔버에서 냉각 챔버로 변환하여 제거할 수 있습니다. EZ LCF를 사용하면 웨이퍼 배치 오류를 방지할 수 있으며, 엄격한 엣지 배제를 통해 클램핑 공정의 성능을 개선하고 다중 챔버 공정 시퀀스와 관련된 적층 오류를 제거할 수 있습니다. 또한 TxZ를 포함한 많은 챔버에 대해 챔버 업그레이드를 사용하여 온칩 균일성을 개선하고 유지 보수를 줄일 수 있습니다.

엔듀라 벤츄라 PVD

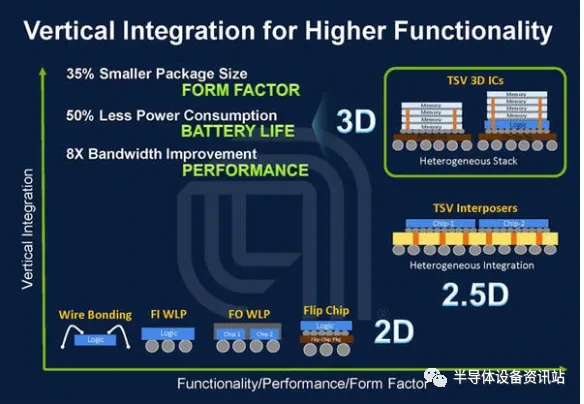

2차원(2D) 디바이스 확장이 물리적, 전기적 한계에 도달함에 따라 TSV 기술은 오늘날 모바일 기술의 확산에서 더 낮은 전력 소비로 더 빠른 성능과 더 큰 기능을 가능하게 하는 컴팩트한 3D(3D) 아키텍처로 전환하는 방법입니다. TSV 기술을 통해 제품 설계자는 적층 칩 또는 웨이퍼를 연결하는 수직 경로를 통해 다양한 노드의 회로 요소를 통합하는 3D 상호 연결을 만들 수 있습니다.

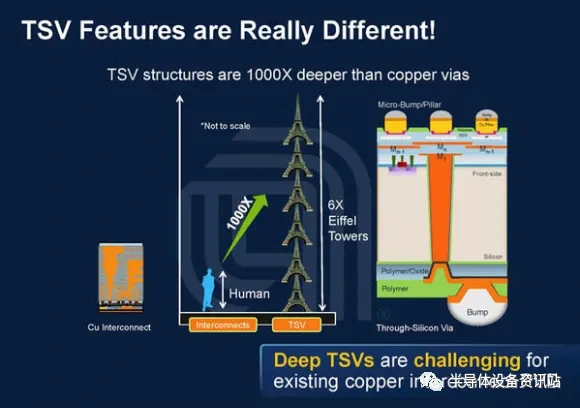

TSV 금속화를 위해 특별히 설계된 어플라이드의 Endura Ventura PVD 시스템은 물리 기상 증착(PVD) 분야의 최신 혁신 기술로, 고객은 2D 모자이크 통합 인프라와 전문 지식을 ≥10:1 종횡비의 TSV 및 2.5D 인터포저 애플리케이션으로 확장할 수 있습니다. 또한 대량 생산 가치가 있는 티타늄 장벽층의 증착을 가능하게 하는 TSV용 최초의 PVD 시스템입니다. 백엔드 공정(BEOL) 애플리케이션을 위한 기존 PVD 시스템은 이러한 높은 종횡비(HAR) 기능을 위해 설계되지 않았으며, 이러한 시스템은 생산 효율성 요구 사항을 충족하기 위해 높은 증착 속도뿐만 아니라 공극 없는 갭 충진 및 우수한 신뢰성이 필요합니다. 갭 메우기 및 장치 신뢰성에 필요한 연속적인 계단식 커버리지를 보장하기 위해 이러한 시스템은 상대적으로 두꺼운 층을 증착해야 합니다. 후막은 비용이 더 많이 들 뿐만 아니라 최종 수율을 감소시킬 수 있는 응력 결함의 위험을 증가시킵니다.

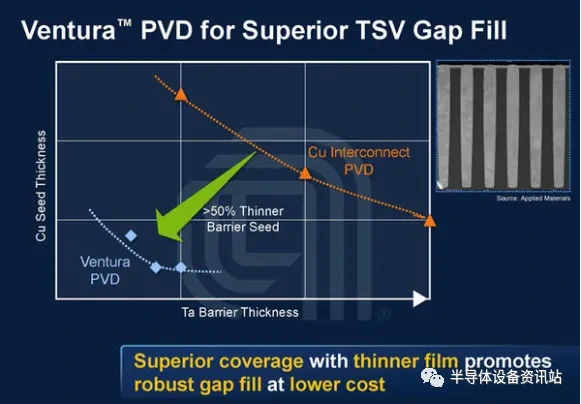

Ventura 시스템은 이러한 TSV 문제를 해결하여 대량 채택에 대한 기술 및 비용 장벽을 크게 줄입니다. 이 시스템은 향상된 이온 밀도, 지향성 및 조정 가능한 에너지를 통합하여 HAR TSV 내부의 BEOL 시스템 층보다 50% 더 얇은 연속 탄탈륨 또는 티타늄 장벽 및 구리 시드 층을 증착하고 생산 비용을 크게 절감합니다. 더 얇은 필름과 더 높은 증착 속도 덕분에 Ventura 시스템은 기존 BEOL PVD 시스템보다 용량을 두 배 이상 늘릴 수 있습니다.

이 시스템을 통해 고객은 원하는 재료를 가공할 수 있습니다. 어플라이드 머티어리얼즈는 이러한 소재를 판매하지 않지만, 벤츄라 챔버는 엔듀라 플랫폼의 구리 시드 레이어 공정과 통합되어 탄탈륨 및 티타늄 장벽 층을 유연하게 처리할 수 있습니다. 두 재료 모두 신뢰성이 높지만 티타늄이 더 비용 효율적입니다.

엔듀라 버사 XLR2 W PVD

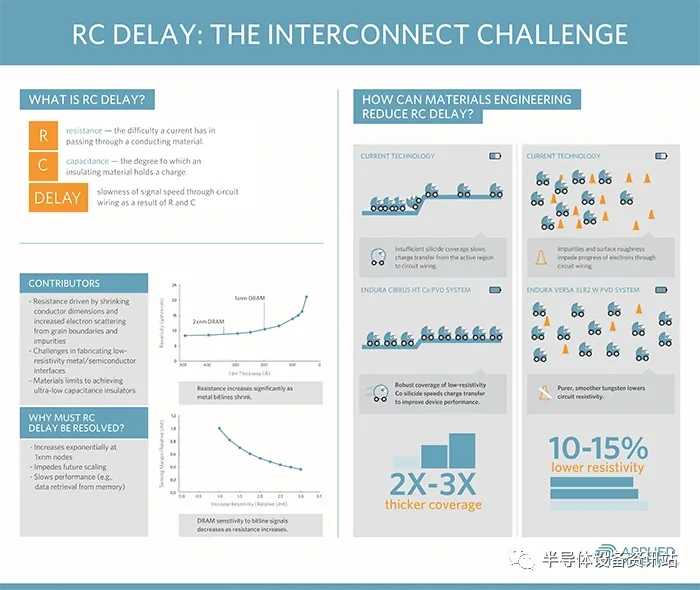

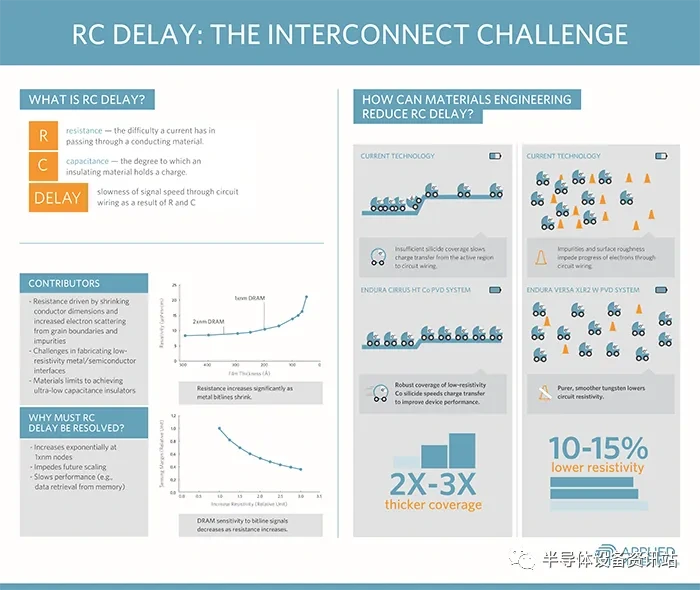

집적 회로와 그 구성 요소가 계속 축소됨에 따라 금속 상호 연결 및 구성 요소 간의 접점도 축소됩니다. 결과적으로 이러한 커넥터의 저항은 점점 더 높아지고 있습니다. 더 작고 더 빠른 전자 장치를 생산하려면 추가 확장을 달성할 수 있도록 저항을 최소화해야 합니다.

이 더 높은 저항으로 인한 조정 효과는 종종 저항-커패시턴스 지연(또는 RC 지연)이라고 하며 다양한 방식으로 회로에 영향을 미칩니다. 이러한 바람직하지 않은 효과 외에도 RC 대기 시간은 비트라인을 통해 DRAM 구조에서 데이터를 읽고 쓰는 속도를 늦출 수 있습니다. 또한 저항이 높을수록 전력 소비가 높아지므로 모바일 기술에 바람직하지 않은 부작용이 발생할 수 있습니다.

와이어의 저항을 줄이는 가장 쉬운 방법은 와이어가 더 넓고 높더라도 전도성 금속의 부피를 늘리는 것입니다. 그러나 더 넓은 와이어는 수축을 제한하고 더 긴 와이어는 커패시턴스를 증가시키고 더 큰 에칭 문제를 제기합니다. 따라서 최첨단 장치의 와이어 저항을 줄이는 것은 전도성 재료의 성능을 향상시키는 데 중점을 둡니다(DRAM 비트 포인트에는 텅스텐(W)이 사용됨).

도체 저항은 전자가 도체를 통과할 때 만나는 산란점의 밀도의 함수입니다. 박막의 불순물, 입자 경계 및 표면 거칠기는 전자 이동 속도를 늦추는 특정 장애물입니다. Versa XLR2 W PVD 캐비티는 현재 기술을 사용하여 증착 된 텅스텐보다 10-15 % 저항이 적은 더 순수하고 부드러운 텅스텐 필름을 증착하여 상호 연결 저항을 줄입니다.

새로운 시스템은 마이크로파 소스 마그네트론, 새로운 공정 화학 및 플라즈마 서명 변조와 같은 주요 하드웨어 구성 요소의 혁신을 통해 이러한 품질 향상을 달성합니다. Versa XLR2 W 시스템에 의해 생성 된 낮은 저항 텅스텐은 스케일링의 조력자이며, 이는 1xnm 노드의 DRAM 기술에서 텅스텐을 비트 메탈로 사용하는 것을 확대 할 것입니다. 다음 애니메이션은 시스템의 뛰어난 박막이 장치의 성능을 향상시킬 수 있는 방법을 설명합니다.

RC 대기 시간은 오늘날의 다재다능한 모바일 소비자 장치의 성능을 개선하는 데 중요한 로직 및 메모리 장치를 지속적으로 축소하는 데 중요한 장벽이 될 수 있기 때문에 매우 중요합니다.

로직 칩과 메모리 칩의 능동 장치(트랜지스터)는 모두 금속 와이어로 서로 또는 칩의 다른 영역에 전기적으로 연결됩니다. 이 전선은 비전도성(절연) 유전층으로 서로 분리되어 있습니다. 로직 및 메모리 칩에서 인터커넥트는 칩의 한 영역에서 다른 영역으로 신호를 전송하는 데 사용됩니다. 가능한 한 빨리 신호를 전송하고 기하학적 소형화로 인한 신호 손실을 최소화하는 기능은 장치 확장에 매우 중요합니다. 로직 칩에서 스케일링은 면적 감소, 즉 재료 및 설계 혁신의 도움으로 더 작은 영역에 점점 더 많은 회로를 패킹할 수 있는 능력을 의미합니다.

비용을 크게 통제해야 하는 가격에 민감한 DRAM 제조 분야에서 확장은 기존 재료 및 설계에서 점진적인 성능을 얻는 데 중점을 둡니다. 요약하면, 로직 및 메모리 와이어의 신호 전송 속도는 동일한 기본 원리에 의해 제어되며 저항 및 커패시턴스(RC)의 곱에 따라 달라집니다. 저항과 정전 용량을 모두 줄이는 것이 이상적입니다. 그러나 정전 용량이 낮은 절연 재료를 개발하고 제조 스트림에 통합하는 데 드는 비용은 메모리 제조업체에게 특히 높습니다.

따라서 저항을 줄이는 것이 스케일링 후 성능을 보장하기 위해 선호되는 방법입니다. 전하가 서로 다른 배선 층을 수직으로 통과하는지 또는 도체의 길이를 따라 가로로 전달하는지에 따라 RC 문제를 해결하기 위해 다양한 솔루션이 필요합니다. 두 경우 모두 목표는 금속 와이어의 저항을 최소화하는 것입니다. 수직 크기에서 솔루션은 계면 저항을 최소화하도록 설계되었습니다. 전기 접점은 작업 영역을 금속 배선 층의 첫 번째 레벨에 연결합니다.

반도체-금속 계면(또는 옴 접촉층)은 활성 영역과 금속 접촉층 사이의 계면을 형성합니다. 목표는 전하가 활성 영역에서 접점을 통해 상부 배선 층으로 그리고 그 반대로 이동할 수 있도록 하는 것입니다. 옴 접촉층 사이의 가장 빠르고 최대화된 전하 전달을 위해서는 낮은 저항률의 재료 층을 형성해야 합니다. 저저항 코발트 규화물은 이러한 목적을 위한 산업 표준으로 채택되었으며 그 효과는 강력한 옴 접촉층을 형성하기 위해 균일한 층을 증착하는 능력에 달려 있습니다.

엔듀라 iLB PVD/ALD

장치의 크기가 줄어들고 통합 개스킷/배리어(iLB) 두께가 더 많은 텅스텐 플러그 부피를 소비함에 따라 접촉 저항이 증가하여 해당 문제가 발생합니다. 센티넬® 증착 챔버가 있는 어플라이드의 Endura iLB PVD/ALD 시스템은 이러한 문제를 해결합니다.

이 시스템은 비용 효율적인 방식으로 ALD(Atomic Layer Deposition) 기술을 활용하여 초박형, 균일한 고품질 배리어 필름의 90% 이상을 덮음으로써 고객의 기존 iLB PVD/CVD 장착 베이스를 32nm 이상으로 확장합니다. 이 제품은 TiN 필름을 증착할 때 플라즈마 손상 또는 유전율이 높은 물질의 특성에 대한 불리한 변화의 위험을 최소화하여 고급 메모리 애플리케이션을 지원합니다.

Centinel 기술은 Endura iLB 통합 PVD/CVD(Physical Vapor Deposition/Chemical Vapor Deposition) 공정 플랫폼을 RE-ALD 챔버(원자 클러스터 강화 원자층 증착 챔버)로 보강하여 32nm 미만 로직 디바이스에서 더 작은 접촉 저항을 달성하여 텅스텐 부피를 최적화합니다. 또한 4X 노드 임베디드 DRAM, DRAM 전극 및 매립 전선 애플리케이션을 위해 설계되었습니다.

Centinel 공정에 의해 달성된 탁월한 계단식 커버리지는 장벽층의 두께를 최소화하여 균일한 침전물의 내부 특성을 최적화합니다. 텅스텐 충전에 사용할 수 있는 부피를 최대화하는 것 외에도 장벽층의 최종 두께는 각 웨이퍼를 처리하는 데 필요한 시간을 줄이고 생산성을 높이는 데 도움이 됩니다. 뒷면 증착이 발생하지 않기 때문에 뒷면 청소로 인해 생산성에 부정적인 영향을 받지 않습니다. 또 다른 이점은 증착 챔버가 더 낮은 가공 온도에서 작동하여 고유전 재료에 대한 재결정 손상을 줄인다는 것입니다.

피카™ PVD

어플라이드의 Pika PVD 시스템은 업계에서 가장 작고 빠른 단일 웨이퍼 PVD 장비로, 낮은 소유 비용으로 고성능 R&D 및 소량 생산이 가능하도록 설계되었습니다. 이 시스템의 컴팩트한 디자인(1657mm x 755mm x 1822mm)에는 탈기, 사전 세척 및 스퍼터 증착 모듈, 고진공 로봇 컨베이어 챔버 및 완전한 박스 투 박스 자동화가 포함됩니다. 92% 이상의 가동 시간으로 높은 수준의 신뢰성을 제공합니다.

이 장치는 금속 및 산화물 합금을 함께 스퍼터링할 수 있는 금속 또는 반응 스퍼터링 공정을 통해 직접, 펄스 직접 및 RF 스퍼터링을 포함한 다양한 PVD 스퍼터링 소스를 지원합니다. D-source 마그네트론 기술은 실리콘, 유리, 유기 재료, 금속, 갈륨 비소 또는 기타 III-V 화합물의 기판에 광범위한 단층 및 다층 필름을 증착하는 입증된 프로세스를 갖추고 있습니다. Pika 시스템의 플러그 앤 플레이 설계는 설정 시간을 최소화합니다.

토파즈™ PVD

어플라이드의 어플라이드 토파즈 PVD 시스템은 PLP(Panel Level Packaging)에 대한 증가하는 수요를 충족하며 선도적인 기술 역량으로 최대 600mm x 600mm의 기판을 처리할 수 있습니다. 저비용, 고성능 전자 장치에 대한 수요로 인해 반도체 산업은 WLP(웨이퍼 레벨 패키징)에서 PLP로 전환하고 있습니다. 표준화된 고정 비용 측면에서 PLP는 웨이퍼 레벨 패키징의 절반에도 미치지 못합니다.

FOWLP(Fan-out Wafer-level Packaging), LCD 및 인쇄 회로 기판을 위해 개발된 공정 기술과 장비의 융합은 팬아웃 패키징 기술을 매우 저렴하게 만듭니다. 이러한 비용 절감을 통해 이 기술은 모바일 전자 장치(예: 시스템 인 패키지, 프로세서, RF 및 전력 관리), 자동차 및 사물 인터넷을 포함한 광범위한 반도체 패키징 응용 분야에서 사용할 수 있습니다.

PLP 외에도 Topaz 시스템은 유리 및 유기 인터포저와 같은 응용 분야를 처리할 수 있을 뿐만 아니라 기판에 다이를 내장할 수 있습니다. 독특한 모듈식 아키텍처는 낮은 접촉 저항을 허용합니다. 필요한 최소 접착 강도를 두 배로 늘리는 단계; 저압; 낮은 기판 온도 (<120C °); 측벽 커버리지가 우수한 컨포멀 시드 층은 에칭 또는 레이저 드릴링에서 형성됩니다.

악셀라 PVD

지난 10년 동안 동급 최고의 Applied Axcela PVD 시스템은 2% 1σ 미만의 불균일성으로 공정 우수성과 안정성을 입증했습니다. 각 스퍼터링 챔버는 장비 소유 비용을 최소화하고, 유지 보수를 용이하게 하고, 최대 8μm 두께의 두꺼운 필름을 형성하고, 세 가지 다른 재료를 증착할 수 있는 기능과 증착 속도를 높이기 위한 공동 스퍼터링 옵션을 표준으로 제공하도록 설계되었습니다. 이 시스템은 컴팩트하며 150, 200, 300 또는 330mm의 다양한 조합으로 구성할 수 있습니다.

이 시스템에는 탈기, 사전 세척 및 PVD 챔버 모듈이 포함되어 있어 광범위한 응용 분야 요구 사항과 최적의 공정 및 처리량 요구 사항을 충족합니다. 이 사용하기 쉬운 시스템 구성 기능을 통해 고객은 특정 애플리케이션에 이상적인 구성을 선택할 수 있습니다.

Axcela 시스템의 저용량 클러스터 아키텍처는 신뢰성이 높은 이 PVD 도구를 EMI 차폐, 후면 금속화, MEMS, TSV, UBM 및 RDL을 포함한 대부분의 금속화 응용 분야에 탁월한 선택으로 만듭니다. 이를 통해 박막의 증착 두께를 엄격하게 제어할 수 있어 공정 및 제조 엔지니어가 까다로운 설계 요구 사항을 충족할 수 있습니다.

D-소스 마그네트론은 전체 부식을 통해 목표 활용도를 향상시킬 수 있습니다. 챔버와 타겟의 아키텍처는 타겟에서 스퍼터링된 원자를 차폐에 낭비하는 대신 수집하는 데 최대 효율성을 허용합니다. 마그네트론과 쉴드의 설계는 시스템의 매우 낮은 입자 수를 용이하게 합니다.

200mm 및 300mm 챔버에 캡슐화된 EMI 링

충전기 UBM PVD

어플라이드의 Charger UBM PVD 시스템은 다이 패키지 금속 증착 공정에서 생산성과 신뢰성에 대한 새로운 기준을 제시합니다. UBM, RDL 및 CMOS 이미지 센서 애플리케이션용으로 설계된 Charger 시스템은 동급 장치보다 두 배 이상의 웨이퍼 수율과 시장에서 가장 높은 생산성을 제공하는 선형 아키텍처가 특징입니다. 또한 이 시스템은 최신 Volaris® 프리 퍼지 기술을 통합하여 서비스 간격으로 더 많은 웨이퍼를 처리하고, 매우 높은 가동 시간을 달성하며, 사용 가능한 웨이퍼당 비용을 가장 낮춥니다.

Volaris 사전 세척 챔버는 유기 멤브레인 탈기로 인한 오염 물질을 최소화하도록 설계되었으며, 기존의 유도 결합 플라즈마 스퍼터링 반응 챔버와 비교하여 기존 응용 분야에서 동급 최고의 접촉 저항 성능을 최첨단 기술 노드로 확장합니다. 이 고유한 clean-in-place 기술은 공정 패키지의 수명을 연장하고 예방적 유지 보수 빈도를 줄여 고객의 패키지 적층 시스템에 대한 생산 비용 절감, 수율 향상 및 소유 비용 최소화를 제공합니다.

최첨단 마그네트론 및 PVD 반응 챔버는 UBM 및 RDL 응용 분야에 사용되는 Ti, TiW, Cu 및 NiV와 같은 광범위한 금속에 대한 엄격한 박막 증착 균일성 사양을 충족하도록 개선되었습니다.

충전기 시스템 온 모듈 아키텍처는 구성 유연성을 향상시켜 컴팩트한 3챔버 구성을 최소한의 다운타임으로 5챔버 대량 제조 시스템으로 쉽게 확장할 수 있습니다.

엔듀라 ALPS PVD (ALPS Co & Ni)

어플라이드의 Endura ALPS(Advanced Low Voltage Source) 코발트 PVD(Physical Vapor Deposition) 시스템은 종횡비가 높은 구조의 게이트 및 콘택트 홀 애플리케이션을 위한 간단한 고성능 금속 규화물 솔루션을 제공합니다. ALPS 기술은 코발트를 90nm 기술 노드 아래로 확장하여 장치에 대한 플라즈마 손상 없이 결함을 최소화하면서 우수한 코발트 바닥 적용 범위를 제공합니다. Endura ALPS Co는 우수한 저항률, 낮은 누설 전류 및 열 안정성을 제공하여 티타늄 응집, 접촉 구멍 저항 변동 및 도펀트 추출과 같은 문제를 해결합니다.

65nm/55nm 노드 이하의 로직 및 스토리지 애플리케이션의 경우 코발트의 실리콘 소비와 실리콘화된 코발트/실리콘 계면의 거칠기가 훨씬 더 중요해집니다. Endura ALPS Ni PVD 시스템은 안정적인 니켈 규화물 필름을 증착하여 실리콘 소비를 2배 줄이고, 필름 인터페이스를 더 매끄럽게 하며, 저항률을 낮춥니다. ALPS Ni는 플라즈마 손상 없이 100Å의 바닥 커버리지를 제공하는 동시에 미립자 수를 최소화합니다.

어플라이드의 Endura ALPS Ni PVD 시스템은 단일 챔버 Siconi Preclean 인터페이스 처리 기술을 사용하여 니켈 규화물(NiSi) 증착 전에 실리콘 표면을 세척할 때 발생하는 문제를 해결합니다.

Siconi Preclean은 높은 선택성 세척(>20:1SiO2:Si, >5:1SiO2)을 제공합니다. : SiN), 기존 HF 세정 공정에 필요한 세정과 니켈 증착 사이의 엄격한 대기 시간 제어의 필요성을 제거합니다. 원격 플라즈마 소스에서 에칭제를 생성하면 기판의 손상을 줄이고 실리콘 질화물 스페이서 및 실리콘 게이트와 같은 구조의 에칭을 최소화할 수 있습니다. 또한 소자 연구에 따르면 Siconi Preclean은 기존 HF 침지 방법에 비해 NiSi2 스파이크 결함을 줄이고 접합부 누출을 개선하는 것으로 나타났습니다.

엔듀라 앰버 PVD

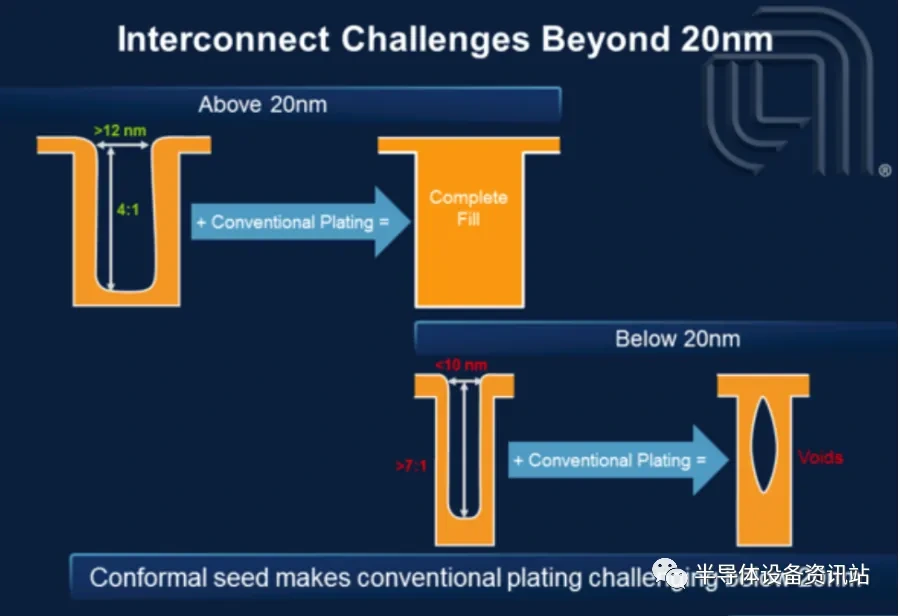

인터커넥트 트렌치와 스루홀 구조를 구리로 안정적이고 완벽하게 채우는 것은 마이크로일렉트로닉스 제조의 장치 신뢰성에 중요합니다. 이 공정에서 필요한 단계는 장벽층(구리가 주변 절연 재료로 퍼지는 것을 방지)과 구리 시드 층(후속 전기화학적 증착(또는 도금)을 용이하게 함)를 증착하여 구멍과 틈이 없도록 하는 것입니다.

현재까지 PVD(Ionized Physical Vapor Deposition)는 모든 도금 표면에서 필요한 적용 두께와 연속성을 달성할 수 있었습니다. 그러나 노드가 2xnm 미만인 경우 볼록한 돌출부가 없는 온전한 커버리지를 가진 최적화된 배리어/시드 레이어 프로세스를 사용하더라도 도금 요구 사항을 충족하기 위해 형상 종횡비를 제어할 수 없습니다.

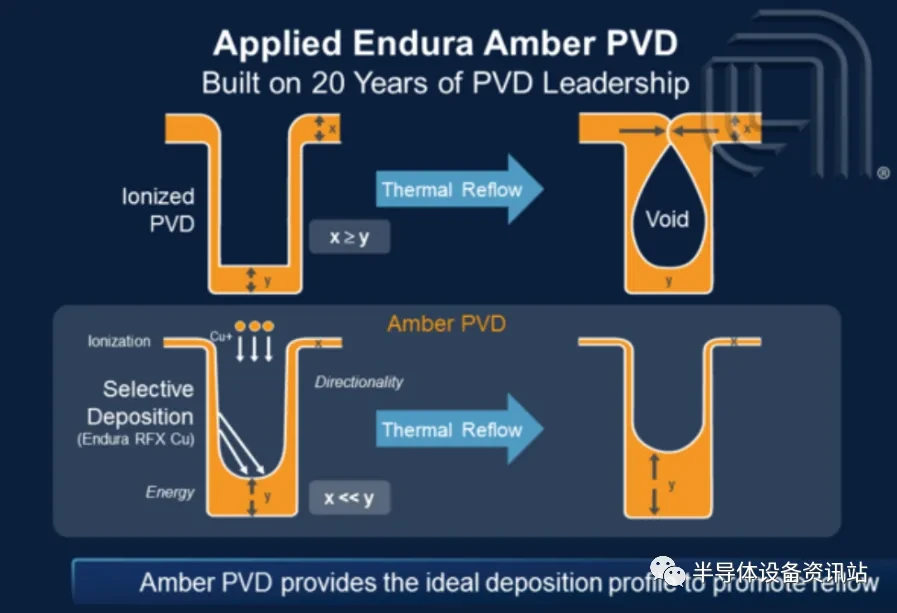

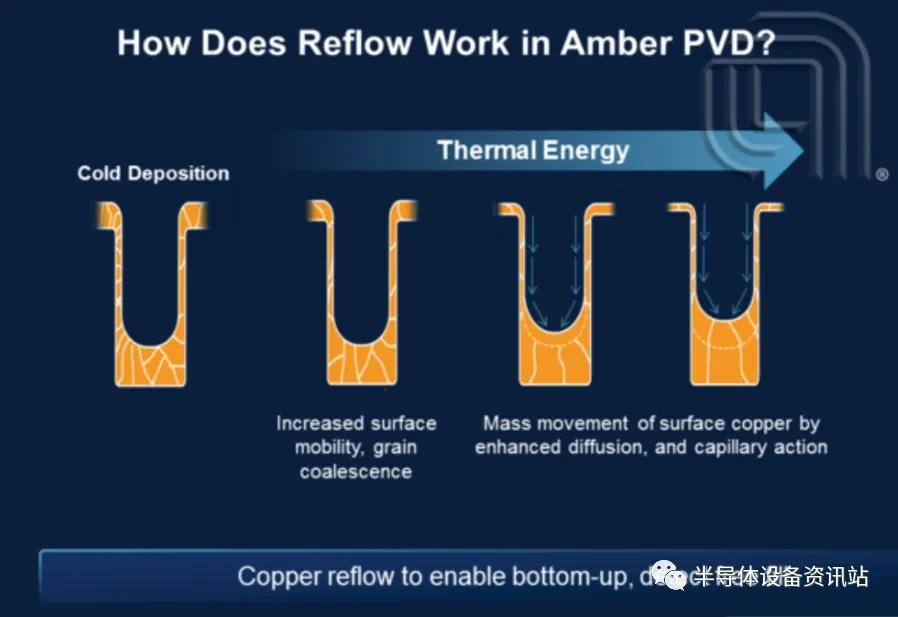

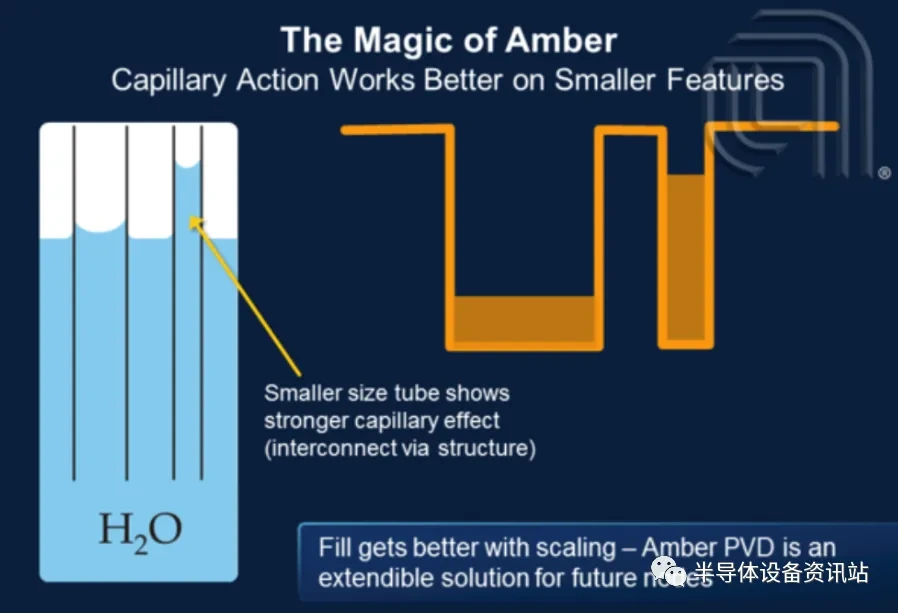

고유한 Endura Amber PVD 시스템은 검증된 통합 접근 방식을 통해 EnCoRe II RFX 구리 시딩 기술을 대체하기 위해 냉간 증착 공정과 고온 고온 구리 리플로우 공정을 결합하여 이러한 문제를 해결합니다. 1xnm 기술 노드에서 구리 오버행은 초소형 스루홀 개구부 주변에서 발생하므로 기존 PVD 공정으로 최적의 도금에 필요한 측벽 및 시드 층 커버리지를 달성할 수 없습니다. 이 새로운 시스템은 상향식 충진을 위한 구리 리플로우를 통해 PVD 증착 공정을 향상시키기 위해 현재 기술의 적용을 확장합니다.

이 2단계 공정은 비아의 유효 종횡비를 줄이거나(한 번 적용) 비아를 완전히 충전(반복 적용)하여 도금 공정을 단순화하여 구멍 없는 충전을 보다 확실하게 하여 장치의 신뢰성을 보장합니다. 증착/리플로우 공정의 각 단계에는 독립적인 온도 제어가 있으며 다양한 개스킷 재료와 유연하게 결합할 수 있습니다.

이 혁신적인 구리 종자 기술은 사전 세척 및 EnCoRe II Ta(N) 배리어 기술을 통해 고진공 조건에서 Endura 플랫폼에 통합되어 대량 생산에서 높은 소자 수율을 가능하게 합니다.

엔듀라 아베니르 RF PVD

높은 종횡비 Ni(Pt) 로직 접점 실리콘화를 위해 시스템은 고전압 정전 용량 결합 플라즈마 모드에서 작동하므로 금속 이온화 밀도가 높아져 하단 커버리지가 향상됩니다.

장치의 크기가 작아지고, 형상이 더욱 취약해지고, 종횡비가 계속 증가함에 따라 현재의 PVD(Physical Vapor Deposition) 기술로는 플라즈마 손상을 방지하기 위해 깊고 좁은 구조를 채우기가 더 어려워지고 있습니다. RF 기반의 저전력 플라즈마를 사용하면 손상 위험을 최소화하고 보다 균일한 플라즈마 밀도 분포를 얻을 수 있어 바닥 적용 범위가 향상되고 균일성이 높아집니다.

Endura Avenir 시스템의 RF PVD는 22nm 이하 노드에서 높은 K/메탈 게이트 애플리케이션과 로직 접촉 실리시드 문제를 해결합니다.

high-K/금속 트랜지스터의 경우 Avenir 시스템은 프론트 게이트 및 포스트 게이트 통합 방식을 위한 다양한 솔루션을 제공하여 칩 제조업체가 두 가지 접근 방식 간에 쉽게 전환할 수 있도록 합니다. 프론트 게이트의 경우, RF PVD 기술은 제어되고 매우 균일한 연속 필름 증착(<10Å)을 가능하게 합니다.

후면 게이트의 경우 고압 용량성 결합 플라즈마 작동을 사용하여 우수한 하단 적용 범위와 최소한의 오버행을 보장할 수 있습니다. 이 시스템의 RF PVD 기술은 초박형 오버레이와 금속 게이트 필름을 증착할 뿐만 아니라 손상 위험을 최소화하여 전하 트랩이 없는 돌연변이 인터페이스를 생성합니다. 이 시스템의 튜닝 기능을 사용하면 필름 균일성을 희생하지 않고 전체 Vt 제어를 위해 TiN 필름을 정밀하게 화학량론으로 제어할 수 있습니다.

효과적인 작업 기능 측면에서 이 요구 사항은 고성능을 달성하기 위해 <4.2eV(NMOS의 경우) 및 >5.0eV(PMOS의 경우)로 변환됩니다. NMOS용 및 고성능 PMOS용 > 5.0eV.

높은 종횡비 Ni(Pt) 로직 접촉 실리사이드의 경우 시스템은 고압 용량성 결합 플라즈마 모드에서 작동하여 더 높은 금속 이온화 밀도와 하단 적용 범위를 달성합니다.

RF PVD 실리콘화 챔버는 기존 PVD Ni(Pt) 공정이 달성한 하단 커버리지의 두 배를 달성하여 5:1 종횡비로 피처 레이어 하단에서 70% 이상의 필드 두께를 가능하게 하고 피처 레이어 내 및 웨이퍼의 중심에서 가장자리까지 일관된 하단 커버리지를 가능하게 합니다. 일관된 하단 적용 범위(3%, 1σ)는 일관된 저항과 낮은 누설률로 변환되며, 높은 백금 부품 균일성은 높은 장치 수율로 이어집니다. 이 시스템은 기존 PVD Ni(Pt) 기술에 비해 소모품 비용을 30% 절감하면서 이러한 성능을 제공합니다.

생산에서 입증된 Endura 플랫폼은 high-K/금속 게이트 및 로직 접점 실리사이드 애플리케이션을 위한 고유한 통합 기능을 제공합니다. 게이트 응용 제품의 경우 PVD, CVD 및 ALD 기술의 전체 제품군을 제공합니다. 접촉층의 경우 Siconi 사전 세척, 실리콘화 및 질화티타늄 오버레이 공정을 결합합니다.

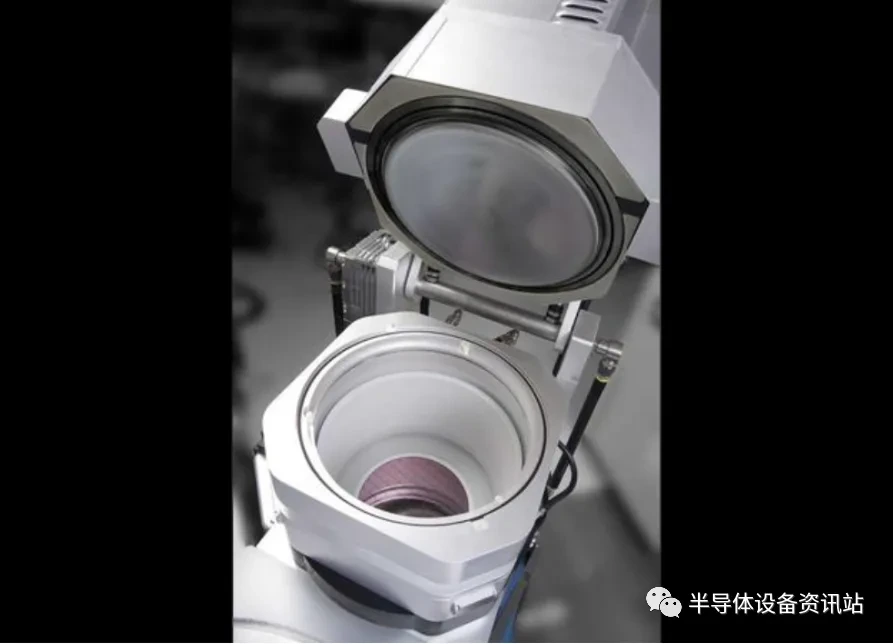

엔듀라 시러스 HT CO PVD

집적 회로와 그 구성 요소가 계속 축소됨에 따라 금속 상호 연결 및 구성 요소 간의 접점도 축소됩니다. 결과적으로 이러한 커넥터의 저항은 점점 더 높아지고 있습니다. 더 작고 더 빠른 전자 장치를 생산하려면 추가 확장을 달성할 수 있도록 저항을 최소화해야 합니다.

이 더 높은 저항으로 인한 조정 효과는 종종 저항-커패시턴스 지연(또는 RC 지연)이라고 하며 다양한 방식으로 회로에 영향을 미칩니다. 이러한 바람직하지 않은 효과 외에도 RC 대기 시간은 비트라인을 통해 DRAM 구조에서 데이터를 읽고 쓰는 속도를 늦출 수 있습니다. 또한 저항이 높을수록 전력 소비가 높아지므로 모바일 기술에 바람직하지 않은 부작용이 발생할 수 있습니다.

스케일링의 또 다른 부작용은 고급 회로의 고유 밀도가 증가함에 따라 종횡비가 증가한다는 것입니다. 결과적으로, 최종 장치가 적절한 전기적 성능을 달성하는 데 필요한 충분한 바닥 커버리지를 가진 박막을 증착하는 것이 점점 더 어려워지고 있습니다. DRAM 구조에서 특히 중요한 것은 활성 영역과 1차 금속 인터커넥트 사이의 반도체-금속 인터페이스입니다. 이러한 계면 간의 가장 빠르고 최대화된 전하 전달을 달성하려면 저항이 낮은 재료(코발트 실리사이드)를 사용해야 하며, 그 효과는 적절한 증착 두께와 균일한 계면층에 따라 다릅니다.

Endura Cirrus HT Co PVD 시스템은 접촉 면적 감소와 종횡비 증가로 인해 발생하는 문제를 해결하기 위해 향상된 기능으로 필요한 규화물 적용 범위를 달성할 수 있습니다. 고주파 RF 소스를 사용하면 다른 소스 기술보다 금속 이온 농도가 높은 플라즈마가 생성되며, 이 시스템은 종횡비가 높은 피처 레이어의 하단에서 우수한 두께와 일관성을 달성합니다. 웨이퍼의 음의 전압은 좁은 구멍에 양극 금속 이온을 도입하는 데 사용되며, 더 많은 금속 이온이 존재하기 때문에 접점 구멍 하단의 적용 범위는 현재 기술로 달성 된 것보다 2 배 또는 3 배 더 두껍습니다. 결과적으로, 코발트 실리사이드의 강력한 층이 형성되어 금속과 반도체 사이의 전하 수송에 대한 장벽을 줄입니다.

이 시스템은 DRAM 주변 회로의 직접 접촉 애플리케이션을 위해 PVD 코발트 및 질화티타늄 캡 증착과 Siconi 실리사이드 사전 세척을 결합합니다.

옴 접촉층의 과제

저장 장치에서 옴 접촉층(반도체-금속 인터페이스)은 활성 영역을 금속 배선 층과 연결합니다. 메모리가 계속 축소됨에 따라 노드 사이의 옴 접촉층 면적이 약 70% 줄어들고 기능 계층에서 종횡비가 증가하며, 이 접촉 층을 형성하기 위해 낮은 저항 규화물이 증착되어야 합니다. 1xnm DRAM에서 이 두 가지 요인으로 인해 전하가 활성 영역에서 접점을 통해 상부 배선층으로 빠르고 안정적으로 이동할 수 있도록 충분히 두꺼운 코발트 규화물 층을 형성하는 것이 점점 더 어려워지고 있습니다.

다음 애니메이션은 옴 접촉층의 개념과 Endura Cirrus HT Co PVD 시스템에서 생성된 두꺼운 규화물 오버레이가 장비 성능에 미치는 유익한 효과를 보여줍니다.

RC 대기 시간은 오늘날의 다재다능한 모바일 소비자 장치의 성능을 개선하는 데 중요한 로직 및 메모리 장치를 지속적으로 축소하는 데 중요한 장벽이 될 수 있기 때문에 매우 중요합니다.

로직 칩과 메모리 칩의 능동 장치(트랜지스터)는 모두 금속 와이어로 서로 또는 칩의 다른 영역에 전기적으로 연결됩니다. 이 전선은 비전도성(절연) 유전층으로 서로 분리되어 있습니다. 로직 및 메모리 칩에서 인터커넥트는 칩의 한 영역에서 다른 영역으로 신호를 전송하는 데 사용됩니다. 가능한 한 빨리 신호를 전송하고 기하학적 소형화로 인한 신호 손실을 최소화하는 기능은 장치 확장에 매우 중요합니다.

로직 칩에서 스케일링은 면적 감소, 즉 재료 및 설계 혁신의 도움으로 더 작은 영역에 점점 더 많은 회로를 패킹할 수 있는 능력을 의미합니다. 비용을 크게 통제해야 하는 가격에 민감한 DRAM 제조 분야에서 확장은 기존 재료 및 설계에서 점진적인 성능을 얻는 데 중점을 둡니다. 요약하면, 로직 및 메모리 와이어의 신호 전송 속도는 동일한 기본 원리에 의해 제어되며 저항 및 커패시턴스(RC)의 곱에 따라 달라집니다. 저항과 정전 용량을 모두 줄이는 것이 이상적입니다.

그러나 정전 용량이 낮은 절연 재료를 개발하고 제조 스트림에 통합하는 데 드는 비용은 메모리 제조업체에게 특히 높습니다. 따라서 저항을 줄이는 것이 스케일링 후 성능을 보장하기 위해 선호되는 방법입니다. 전하가 서로 다른 배선 층을 수직으로 통과하는지 또는 도체의 길이를 따라 가로로 전달하는지에 따라 RC 문제를 해결하기 위해 다양한 솔루션이 필요합니다. 두 경우 모두 목표는 금속 와이어의 저항을 최소화하는 것입니다.

수직 크기에서 솔루션은 계면 저항을 최소화하도록 설계되었습니다. 전기 접점은 작업 영역을 금속 배선 층의 첫 번째 레벨에 연결합니다. 반도체-금속 계면(또는 옴 접촉층)은 활성 영역과 금속 접촉층 사이의 계면을 형성합니다. 목표는 전하가 활성 영역에서 접점을 통해 상부 배선 층으로 그리고 그 반대로 이동할 수 있도록 하는 것입니다.

옴 접촉층 사이의 가장 빠르고 최대화된 전하 전달을 위해서는 낮은 저항률의 재료 층을 형성해야 합니다. 저저항 코발트 규화물은 이러한 목적을 위한 산업 표준으로 채택되었으며 그 효과는 강력한 옴 접촉층을 형성하기 위해 균일한 층을 증착하는 능력에 달려 있습니다. 횡방향 치수에서 이 솔루션은 와이어 금속 재료의 전도성을 최적화하도록 설계되었습니다. 소위 선형 저항은 와이어 크기(너비, 높이, 길이)와 와이어 준비 재료(일반적으로 텅스텐 또는 구리)의 특정 특성의 함수입니다.

와이어의 저항을 줄이는 가장 쉬운 방법은 와이어가 더 넓고 높더라도 전도성 금속의 부피를 늘리는 것입니다. 그러나 더 넓은 와이어는 수축을 제한하고 더 긴 와이어는 커패시턴스를 증가시키고 더 큰 에칭 문제를 제기합니다. 따라서 최첨단 장치의 전선 저항을 줄이는 것은 전도성 재료의 성능을 향상시키는 데 중점을 둡니다.

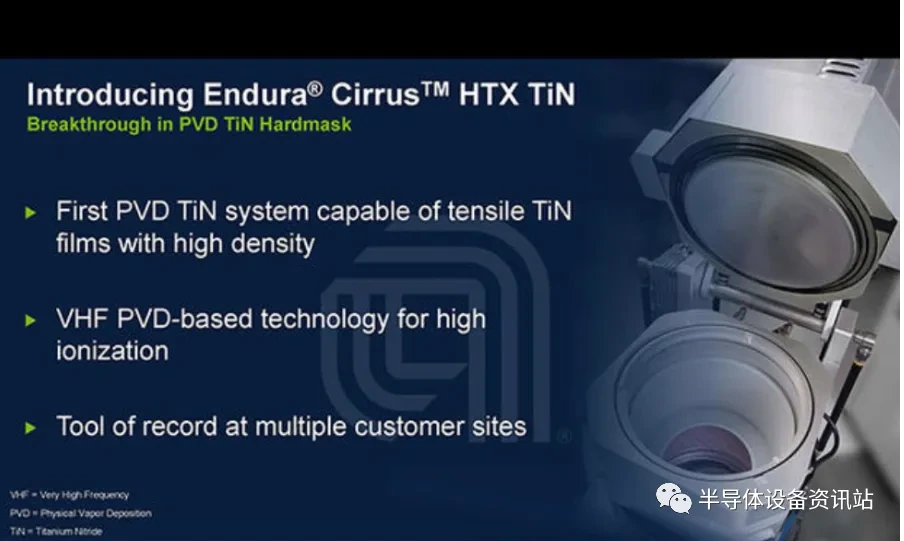

엔듀라 시러스 HTX PVD

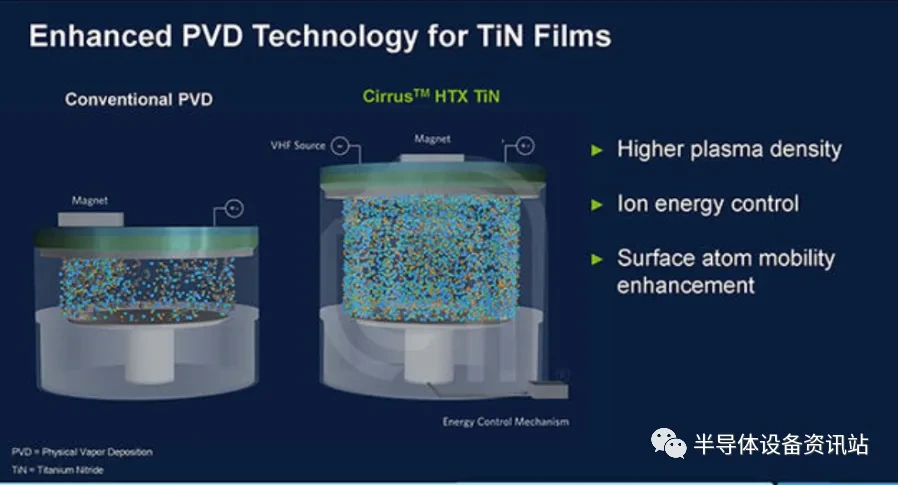

질화 티타늄(TiN) 필름에 대한 PVD(물리적 기상 증착) 기술에 혁명을 일으킴으로써 Endura Cirrus HTX TiN은 차세대 장치의 하드 마스크 확장성 문제를 해결합니다. 칩 피처 크기가 더욱 축소됨에 따라 더 복잡한 작은 인터커넥트 구조의 정확한 패터닝을 위해서는 하드마스크 혁신이 매우 중요합니다. PVD에 대한 수년간의 전문 지식을 바탕으로 한 이 새로운 시스템은 10nm 미만 노드에서 패턴 충실도를 보장하는 획기적인 하드 마스크를 생산합니다.

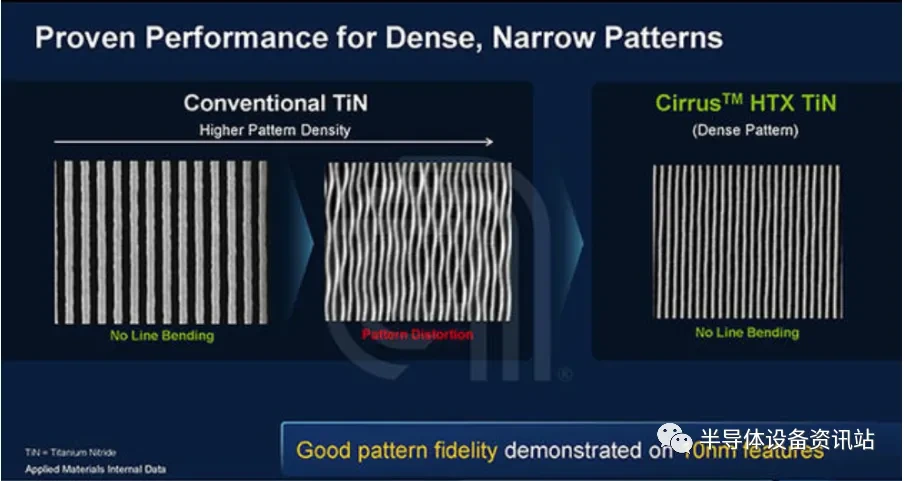

칩 설계가 발전함에 따라 칩은 고급 집적 회로를 생산하기 위해 피처 크기가 더 작아지고 종횡비가 높아지며 패키지 밀도가 더 높아졌습니다. 결과적으로, 에칭 및 금속화 패턴을 정의하는 데 사용되는 재료는 회로(또는 상호 연결)를 생성할 때 이러한 패턴의 무결성을 유지하는 데 매우 중요합니다. 사소한 결함으로 인해 장치를 적절하게 금속화할 수 없어 신뢰할 수 없거나 작동하지 않을 수 있습니다.

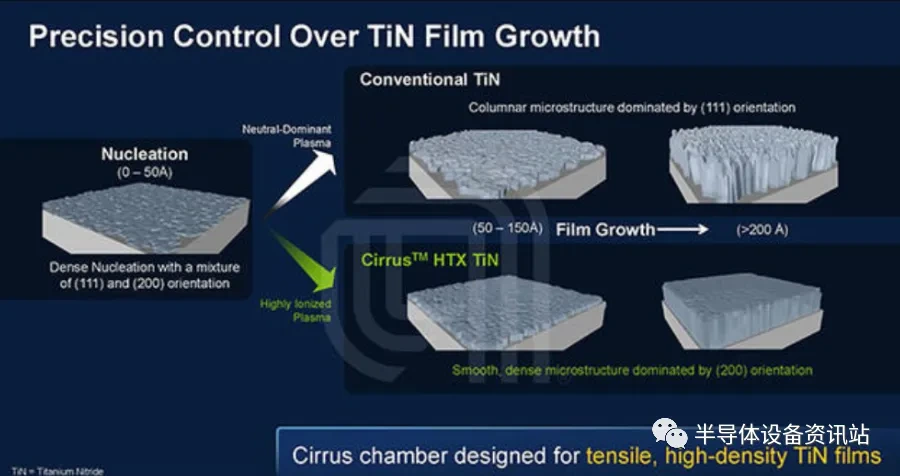

질화티타늄(TiN)은 인터커넥트 제조 공정에서 low-K 유전체 패터닝을 위한 표준 하드마스크 소재입니다. 그러나 고급 노드에서 유전체는 소자 커패시턴스를 줄이기 위해 점진적으로 더 다공성으로 만들어지므로 중첩된 TiN 마스크의 압축 응력으로 에칭(라인 굽힘 및 패턴 붕괴) 후 더 취약하고 변형되기 쉽습니다. 이러한 자연적인 압축 응력을 제거하면 필름의 밀도가 감소하지만 에칭 공정을 견뎌야 합니다.

주요 돌파구로, Endura Cirrus HTX PVD 시스템은 초고주파 RF 소스를 사용하여 박막의 결정화 배향을 용이하게 하는 고도로 이온화된 플라즈마를 생성함으로써 응력과 밀도 간의 까다로운 균형을 해결합니다. 그 결과 TiN은 인장 응력 저항과 고밀도의 이상적인 조합을 달성하여 우수한 식각 선택성, 우수한 CD 선폭 제어 및 스루홀 스택 정렬, 조밀하고 복잡한 패턴의 높은 충실도를 제공합니다. 우수한 필름 두께 균일성과 낮은 결함률로 인해 새로운 시스템은 변동성을 줄이고 매우 정확한 패턴을 생성할 수 있습니다.

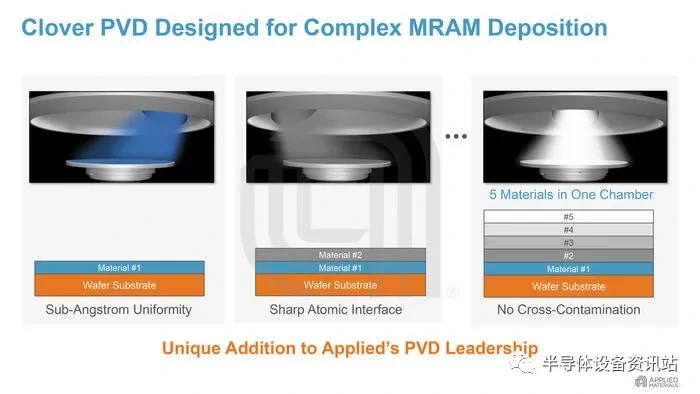

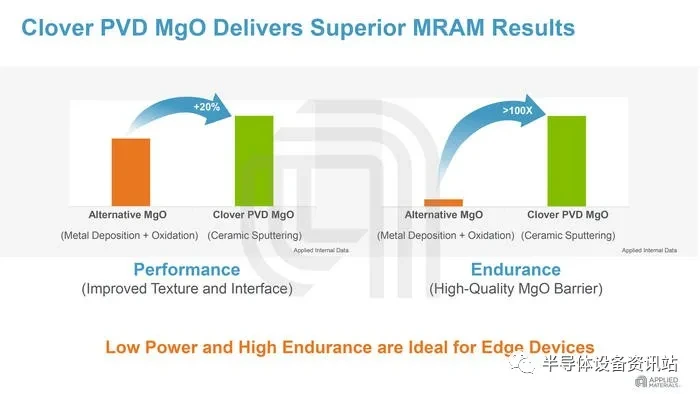

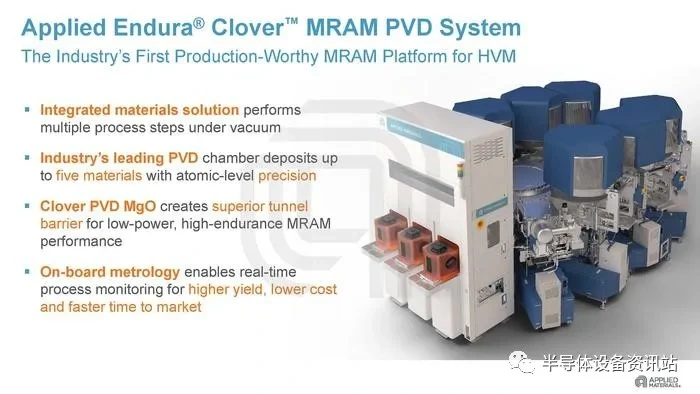

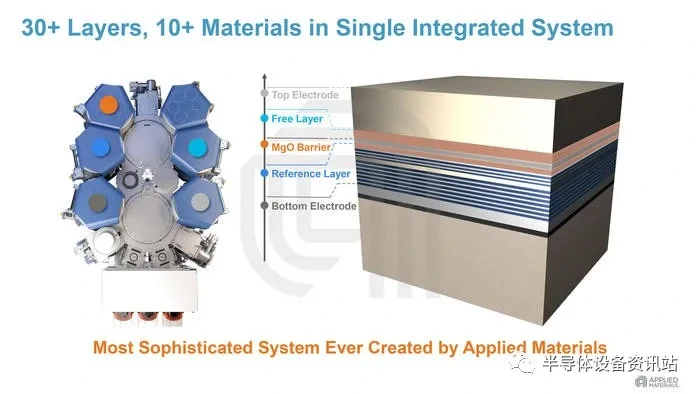

엔듀라 클로버 MRAM PVD

어플라이드의 Endura Clover MRAM PVD 시스템은 MRAM(Magnetic Random Access Memory) 장치의 대량 생산(HVM)을 위한 최초의 생산 가치 있는 통합 재료 솔루션입니다™. 플래시 메모리의 전하 기반 특성으로 인해 확장 제한이 적용됩니다. MRAM은 저항기 기반 작동이 확장성이 뛰어나고 메모리 반도체에서 기대할 수 있는 주요 특성인 비휘발성, 랜덤 액세스 및 견고한 견고성을 제공하기 때문에 가장 유망한 대안입니다.

엔듀라 CuBS RFX PVD

어플라이드의 Endura CuBS(Copper Barrier/Seed) RF XT PVD 시스템은 3x/2x 노드 이상의 로직 및 메모리 애플리케이션에 사용됩니다. SIP(Autoionized Plasma) EnCoRe II Ta(N) 장벽층 및 EnCoRe II RFX 구리 시드층 처리 챔버는 고도의 이온화 PVD 기술을 사용하여 최소한의 돌출부와 부드러운 형태로 완전히 덮인 저온 박막 증착을 가능하게 합니다.

EnCoRe II Ta(N) 캐비티의 두께 조정 기능을 통해 고객은 장벽층의 두께를 줄여 선형 저항을 3x/2x 노드 수준까지 낮추는 동시에 우수한 하단 및 측벽 오버레이로 일렉트로마이그레이션 및 응력 이동을 줄일 수 있습니다. 구리 시드 층의 경우, EnCoRe II RF XT Cu cavity는 혁신적인 마그네트론 모션, 자속 제어 및 높은 레스퍼터링 비율 메커니즘을 통합하여 동형 커버리지를 더욱 향상시킵니다.

이러한 기술은 웨이퍼 가장자리의 라인 말단 다공성 또는 CMP 처리 후 결함과 같이 금속 보이드 충전의 품질을 저하시킬 수 있는 문제를 완화합니다.

기하학적 치수의 감소에 수반되는 점점 더 중요해지는 인터페이스 문제를 해결하기 위해 어플라이드 머티어리얼즈는 중요한 치수나 재료 특성을 손상시키지 않으면서 인터페이스 무결성을 보장하는 다양한 사전 세척 기술을 제공합니다. Endura CuBS RF XT 시스템은 Black Diamond® II와 같은 다공성의 저 k-order 유전체 필름을 보호하면서 폴리머 잔류 물을 효과적으로 제거하고 CuO를 줄이는 획기적인 사전 세척 기술을 제공하는 새로운 Aktiv Preclean 방법을 사용합니다. 기존의 반응성 사전 세척 방법과 달리 Aktiv Preclean 공정은 k-값을 크게 변경하지 않으므로 차세대 low-k 유전체층으로의 전환을 용이하게 합니다.

어플라이드의 Endura CuBS RF XT PVD 시스템은 고진공 조건에서 Ta(N)/Ta 장벽층을 순차적으로 증착한 후 구리 시드 층을 증착합니다. 새로운 Aktiv Preclean을 포함한 Endura 플랫폼에 모든 제품을 통합함으로써 우수한 필름 접착력 및 무산화물 인터페이스가 보장되는 동시에 낮은 스루홀 저항과 높은 장치 신뢰성을 위한 k-값 무결성을 유지합니다.

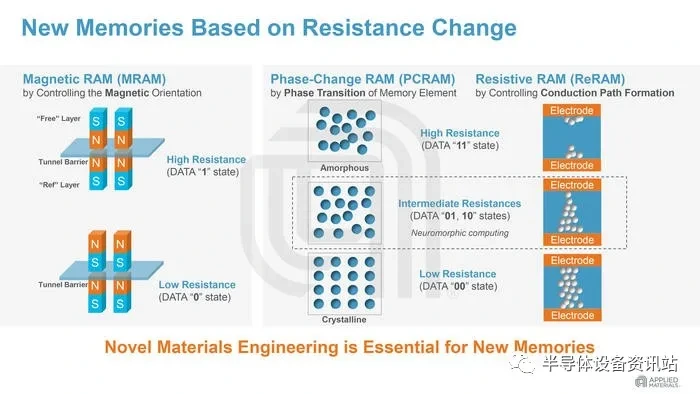

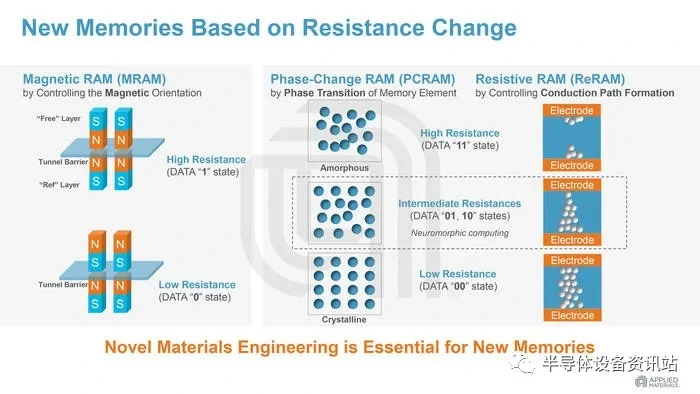

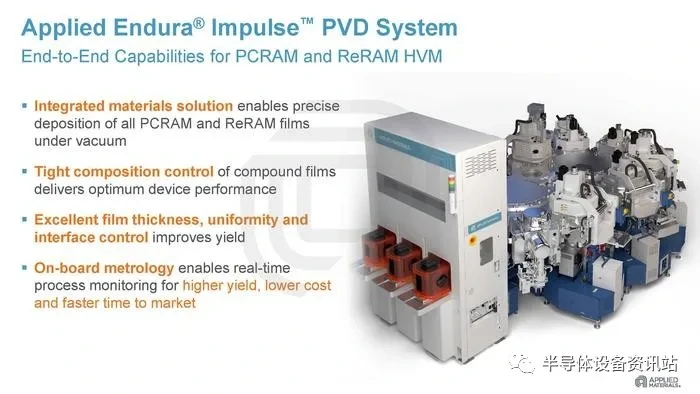

엔듀라 임펄스 PCRAM PVD

어플라이드 머티어리얼즈(Applied Materials)의 Endura Impulse PVD 시스템은 위상 변화 랜덤 액세스 메모리(PCRAM) 및 저항성 랜덤 액세스 메모리(ReRAM) 장치의 대량 생산(HVM)을 위한 생산 가치가 있는 통합 재료 솔루션입니다™. PCRAM과 ReRAM은 DRAM(데이터 처리용)과 NAND(데이터 저장용) 사이의 가격 대비 성능 격차를 해소하는 새로운 비휘발성 메모리입니다. PCRAM 및 ReRAM은 스토리지 및 검색 속도, 전력 효율성 및 안정성을 개선하여 정전 시에도 소프트웨어와 데이터를 보존할 수 있습니다.

엔듀라 아이오닉 W PVD

집적 회로와 그 구성 요소가 계속 축소됨에 따라 금속 상호 연결 및 구성 요소 간의 전선 크기도 축소됩니다. 그 결과, 이러한 상호 연결 구조는 점점 더 저항력이 높아지고 있습니다.

이 높은 저항은 종종 저항기 커패시턴스 지연(또는 RC 지연)이라고 하는 조정 효과를 생성하여 전도 속도를 줄이고 전력 손실을 증가시켜 칩 성능에 영향을 줄 수 있습니다. 보다 컴팩트하고 빠른 전자 장치를 만들기 위해서는 이러한 연결의 저항을 최소화하여 더 축소할 수 있어야 합니다.

어플라이드의 새로운 엔듀라 아이오닉 PVD 시스템은 통합 소재 솔루션™이다(Integrated Material Solutions)는 첨단 제조 공정과 CVD 기술 및 고진공 플랫폼의 전처리 챔버를 결합하여 다양한 와이어 응용 분야에서 순수 텅스텐(W) 재료 금속화를 달성합니다. 단일 티타늄 질화물 기판, 텅스텐 핵 형성 층 및 벌크 텅스텐 필러를 높은 저항으로 대체하여 여러 기계를 완료해야하며 CVD 벌크 텅스텐 필러와 융합 된 단일 PVD 텅스텐 층을 사용합니다.

아이오닉 PVD 챔버의 향상된 이온화 및 방향 흐름 제어는 순수 텅스텐 필름의 우수하고 균일한 계단식 코팅을 통해 낮은 저항을 위한 장벽 및 라이너 역할을 합니다. 지속적인 고진공 환경은 필름의 무결성을 유지하여 금속 계면의 순도와 전도성을 더욱 향상시킵니다.

어플라이드의 엔듀라 아이오닉 PVD 시스템은 로직 애플리케이션의 중요 와이어에서 텅스텐(W) 사용을 5nm 미만으로 확장하는 동시에 DRAM 및 NAND 소자의 저저항 연결을 위한 고유한 금속화 방법을 제공하여 소자 소형화를 더욱 발전시키는 데 도움이 됩니다.

'Semiconductor' 카테고리의 다른 글

| CMOS Process Flow (코모스 프로세스 흐름) (0) | 2025.01.24 |

|---|---|

| 반도체 제조 Track(트랙) - ADH, COT, DEV, LHP, CPL, (0) | 2025.01.24 |

| 어플라이드 머티어리얼즈 (Applied Materials) - 3부 (0) | 2025.01.24 |

| 어플라이드 머티어리얼즈 (Applied Materials) - 2부 (0) | 2025.01.24 |

| 어플라이드 머티어리얼즈 (Applied Materials) - 1 부 (0) | 2025.01.24 |

댓글