글로벌 시장 동향,

산업기술개발 로드맵, ESG

ASML은 사회가 "어디에나 있는 칩"에서 "어디에나 있는 AI 칩"의 새로운 시대로 이동하고 있다고 믿습니다. 차세대 AI 기술은 무한한 기회를 제공하며, AI는 2030년까지 전 세계 GDP에 6조 달러에서 13조 달러를 추가할 것으로 예상됩니다.

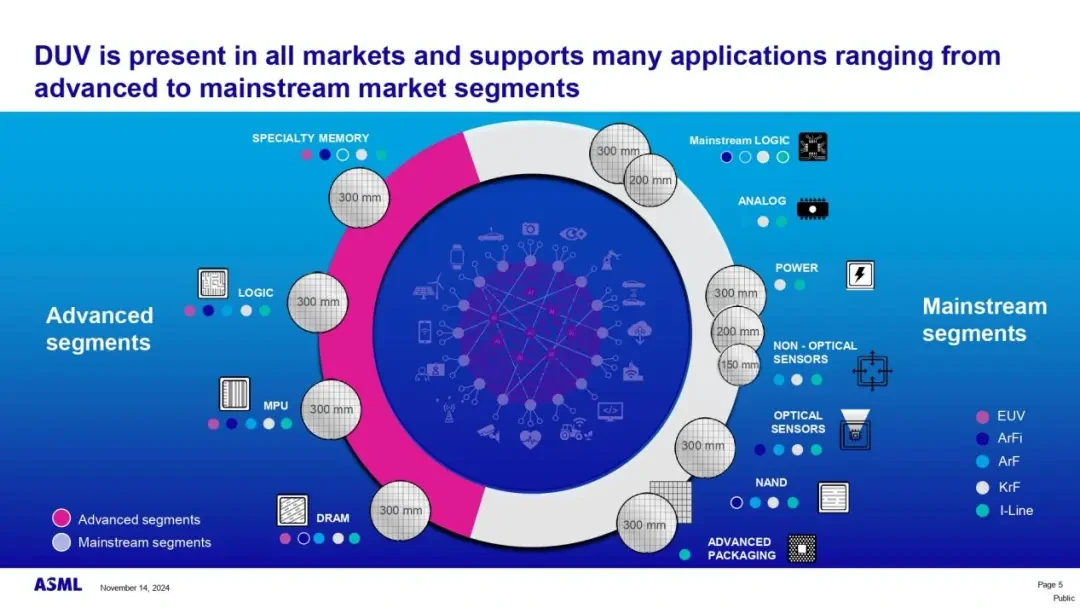

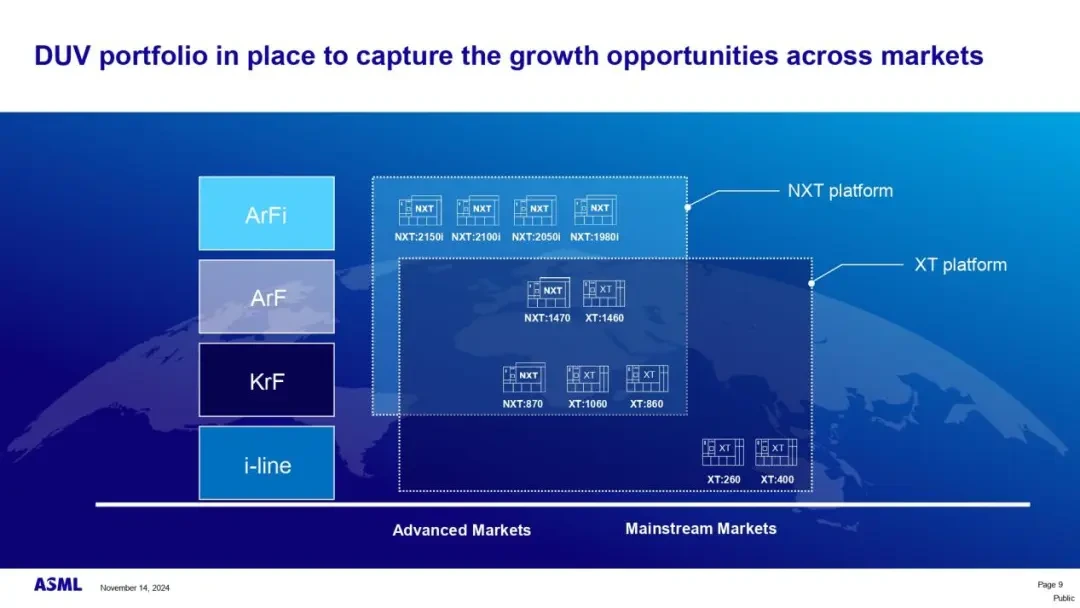

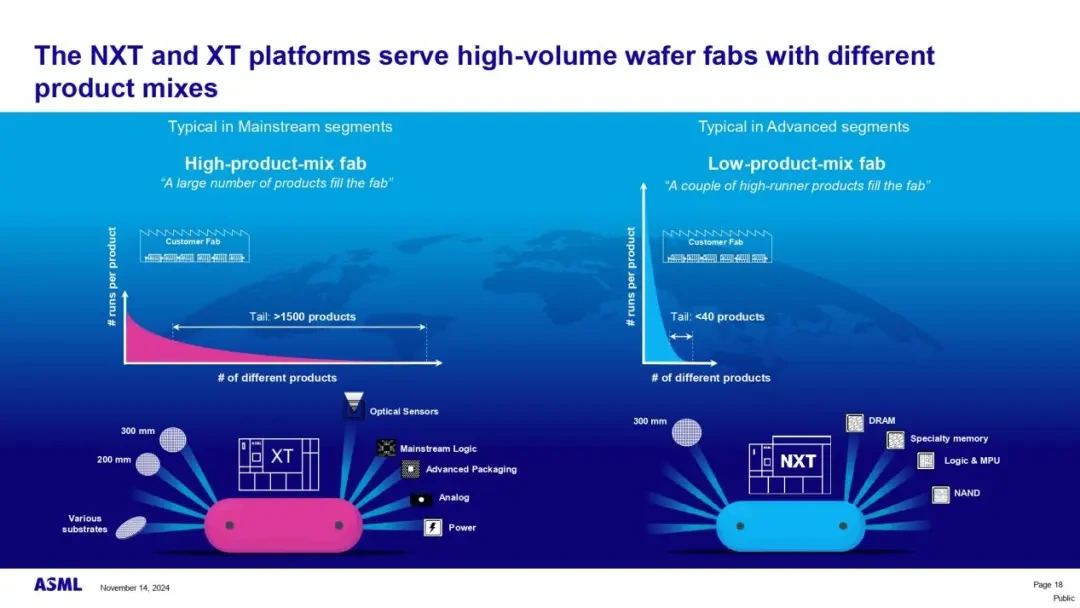

자율 주행 및 스마트 홈에서 의료 및 산업 자동화에 이르기까지 AI의 확산은 고성능 컴퓨팅에 대한 수요를 주도할 뿐만 아니라 주류 시장의 성장에도 박차를 가하고 있습니다. 현재 주류 시장에서 칩에 대한 수요는 특히 고성능 칩 분야에서 꾸준히 증가하고 있으며, 이는 여전히 기술 진보의 무어의 법칙을 따릅니다. 반도체 시장은 "첨단 분야"와 "주류 분야"의 두 부분으로 나눌 수 있습니다 .

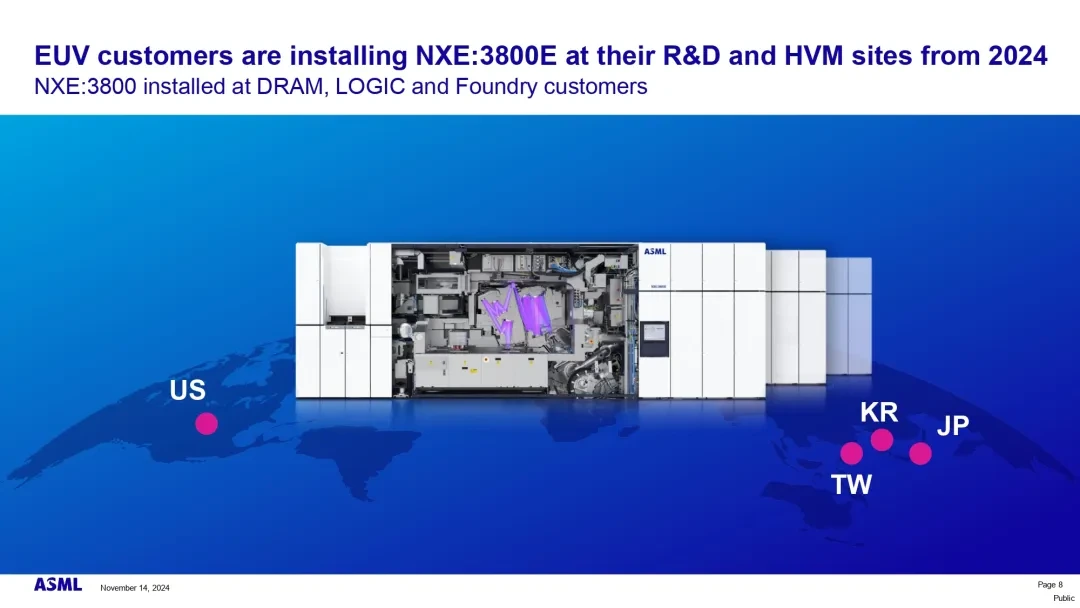

첨단 분야는 주로 로직 칩, MPU (마이크로 프로세서) 및 DRAM과 같은 고급 응용 분야를 포함하며 극자외선 리소그래피 (EUV)와 같은 고급 공정에 크게 의존하며 응용 시나리오는 미국, 한국, 대만 및 기타 기술 프런티어 지역에 집중되어 있습니다. 주류 분야는 주로 ArFi, ArF, KrF 및 I-Line과 같은 리소그래피 기술을 사용하여 아날로그 칩, 전력 칩, 센서, NAND 플래시 메모리 및 기타 일일 수요가 많은 칩 제품을 포함하며 유럽, 일본, 중국 및 기타 주요 반도체 소비자를 포괄하는 광범위한 지역 분포를 가지고 있습니다.

ASML은 2030년까지 글로벌 반도체 매출이 1조 달러를 넘어설 것이라는 기대를 재차 강조했다. AI에 대한 상당한 투자가 계속되고 있지만 소비자 제품에 얼마나 빨리 채택될지에 대해서는 여전히 불확실성이 있습니다.

반도체 생태계는 장기적인 혁신과 성장을 주도하기 위해 EBIT(이자 및 세금 전 이익)의 약 절반을 재투자했으며, ASML은 이러한 추세가 계속될 것으로 예상합니다.

(출처: Corporate Marketing (CMKT) analysis; 회사 보고서; 참고: EBIT = 이자 및 세금 차감 전 이익.)

무어의 법칙에 대한 AI의 추진

무어의 법칙(Moore's Law)은 계산 성능 분야에서 여전히 살아 있습니다. 각 패키지의 트랜지스터 수는 여전히 2년마다 두 배씩 증가하고 있으며 2030년까지 1조 개의 트랜지스터에 이를 것으로 예상됩니다. ASML은 생성형 AI의 개발이 무어의 법칙의 발전을 가속화할 것으로 기대하고 있습니다. 생성형 AI와 고성능 컴퓨팅(HPC)은 무어의 법칙보다 더 빠르게 성장하고 있으며, 고성능 컴퓨팅에 대한 수요는 2년마다 16배씩 증가하고 있습니다. 2030년까지 데이터센터 수요의 70% 이상이 AI에 의해 주도될 것으로 보이며, 생성형 AI는 컴퓨팅 수요(FLOP)의 90% 이상을 차지할 것으로 예상됩니다.

AI의 잠재력을 최대한 발휘하기 위해 슈퍼컴퓨터 아키텍처는 AI의 요구 사항을 충족해야 합니다. 현재 Aurora 슈퍼컴퓨터로 대표되는 고성능 컴퓨팅 플랫폼은 21,248개의 CPU, 63,744개의 GPU, 10,624개의 노드를 포함하는 2페타플롭스의 부동 소수점 컴퓨팅 파워(FLOP)를 제공할 수 있습니다. 메모리 측면에서는 10.9PB의 DDR 용량, 1.36PB의 HBM CPU 용량, 8.16PB의 HBM GPU 용량을 갖추고 있어 최대 208.9PB/s의 피크 대역폭을 지원합니다. 스토리지 측면에서 Aurora 슈퍼컴퓨터는 230PB의 용량과 31TB/s의 대역폭을 갖추고 있으며 1,024개의 DAOS 노드가 있어 시스템의 효율적인 스토리지 및 데이터 전송 용량을 보장합니다.

그러나 대량 채택을 달성하기 위해서는 Aurora 슈퍼컴퓨터 구축 비용이 이미 5억 달러 이상이었기 때문에 컴퓨팅 아키텍처 비용을 줄이는 것이 시급합니다. 이 외에도 급격히 증가하는 에너지 소비도 주요 과제입니다. 이를 해결하지 않으면 에너지 소비 문제로 인해 향후 훈련 능력이 제한될 수 있습니다. 예를 들어, Aurora 슈퍼컴퓨터는 초당 2조 작업(FLOP)을 제공하면서 60메가와트(MW) 이상의 전기를 소비하고 지속적인 작동을 위해 분당 34,000갤런의 냉각수를 소비합니다. 컴퓨팅 수요와 GPU 수가 증가함에 따라 데이터 센터의 에너지 소비는 특히 100,000 GPU 수준에서 기하급수적으로 증가하고 있습니다. 이러한 추세가 계속된다면 대규모 AI 훈련은 향후 에너지 소비 병목 현상에 직면하게 될 것입니다.

출처:Lisa Su, AMD, ITF 2024년 5월 21일

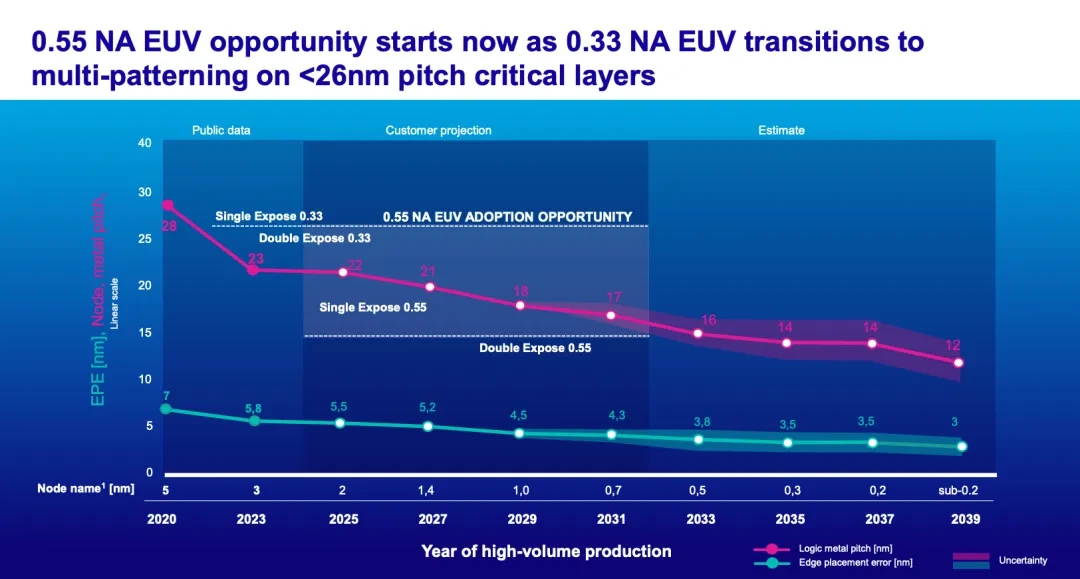

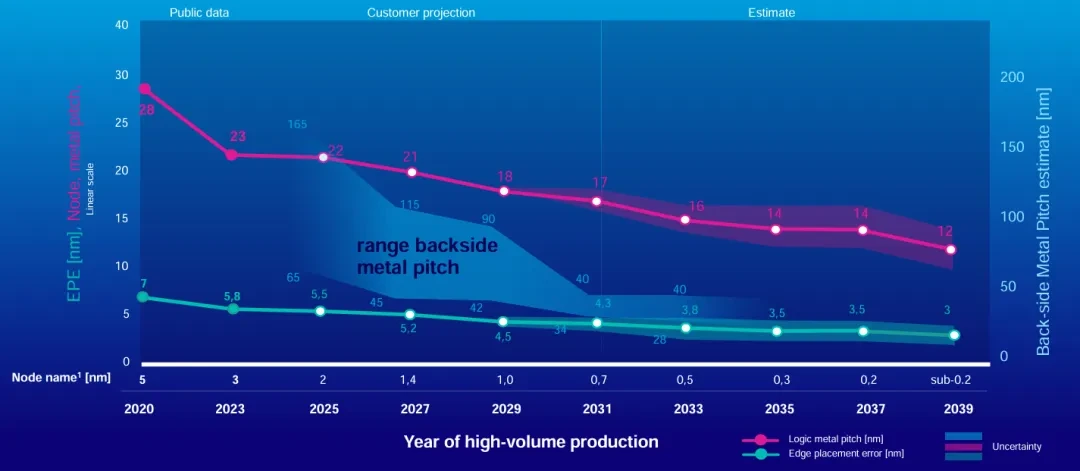

ASML은 반도체 제조업체가 칩 확장을 계속 추진할 것으로 예상하며, 트랜지스터 크기를 줄이는 것이 여전히 비용을 절감하고 밀도를 높이는 가장 쉬운 방법일 수 있습니다. 인공 지능에 대한 수요에 힘입어 반도체 기술의 논리적 로드맵은 계속 가속화되어 다차원적 혁신을 통해 더 높은 성능과 더 작은 칩을 가능하게 할 것입니다. 기술 노드의 경우, 2018년 N7 프로세스를 시작으로 향후 N5, N3, N2 등 고급 노드로 점차 발전해 2039년까지 Sub-A2 수준에 도달할 것으로 예상됩니다.

출처:1Luc van den Hove, IMEC , ITF May 21, 2024

칩 제조의 기술 진화 경로는 주로 세 가지 측면에서 시작됩니다.

- 장치 및 재료 혁신: FinFET(FinFET(FinFET 트랜지스터) 기술)에서 시작하여 점차 NanoSheet 및 CFET(Complementary FET) 구조로 전환하고 있으며 최종적으로 향후 가능한 2DFET로 전환하고 있습니다. 기술의 각 단계는 성능을 개선하고 크기를 줄이기 위해 도입, 확장 및 최적화되어 더 높은 트랜지스터 밀도를 가능하게 합니다.

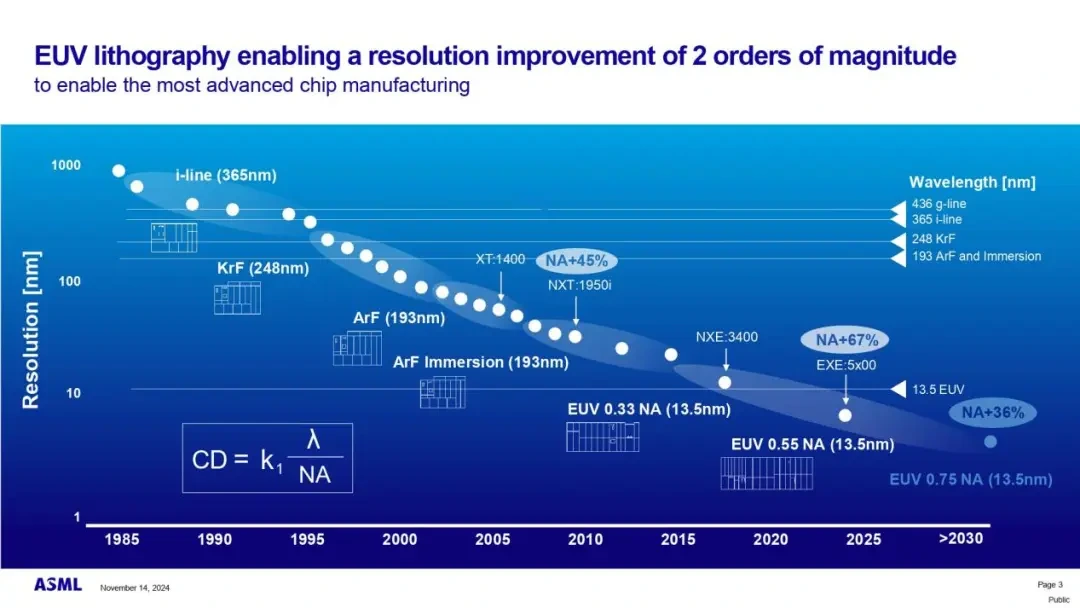

- 지속적인 크기 확장: 기술 노드가 발전함에 따라 금속 피치는 초기 40nm에서 2039년까지 10nm 미만으로 줄어들고 있습니다. 동시에 EUV 리소그래피(극자외선 리소그래피)는 지속적으로 최적화되어 향후 새로운 0.33NA, 0.55NA 및 0.75NA EUV 기술을 도입하여 고정밀 제조의 요구를 충족시킬 것입니다.

- 칩 인터커넥트 아키텍처: 글로벌 인터커넥트에서 로컬 신호 라인에 이르기까지 후면의 금속 간격을 점차 줄여 칩의 전반적인 성능과 전력 효율성을 더욱 향상시킵니다. 이러한 인터커넥트 아키텍처의 진화는 미래의 AI 애플리케이션에 더 큰 컴퓨팅 성능을 제공하는 더 복잡한 칩 설계를 가능하게 합니다.

미래의 2차원(2D) 및 3차원(3D) 혁신은 향후 15년 동안 반도체 기술의 지속적인 발전을 위한 토대를 마련할 것입니다

AI는 DRAM 아키텍처와 용량의 변화를 주도하고 있습니다.

기존의 von Neumann 아키텍처는 처리 장치를 저장 장치와 분리하기 때문에 빈번한 데이터 전송이 발생하여 시스템의 효율성을 제한합니다. 새로운 PIM(Processing In Memory) 기술은 처리 장치를 메모리 모듈에 직접 통합하여 속도와 에너지 효율성을 크게 향상시킵니다.

SK하이닉스는 대역폭을 10배 향상하는 것은 물론 전력 효율도 7배 향상하는 GDDR6 기반 AiM(Accelerator in Memory) 칩을 선보였는데, 이 칩은 AI 및 고연산 밀도 애플리케이션에서 메모리 성능을 대폭 최적화했다. PIM 기술의 도입은 향후 DRAM의 근본적인 혁명을 예고하며, 이는 메모리 집약적인 작업에 대한 더 강력한 지원을 제공하여 전체 시스템이 성능과 에너지 효율성 면에서 새로운 차원에 도달할 수 있도록 할 것으로 예상됩니다.

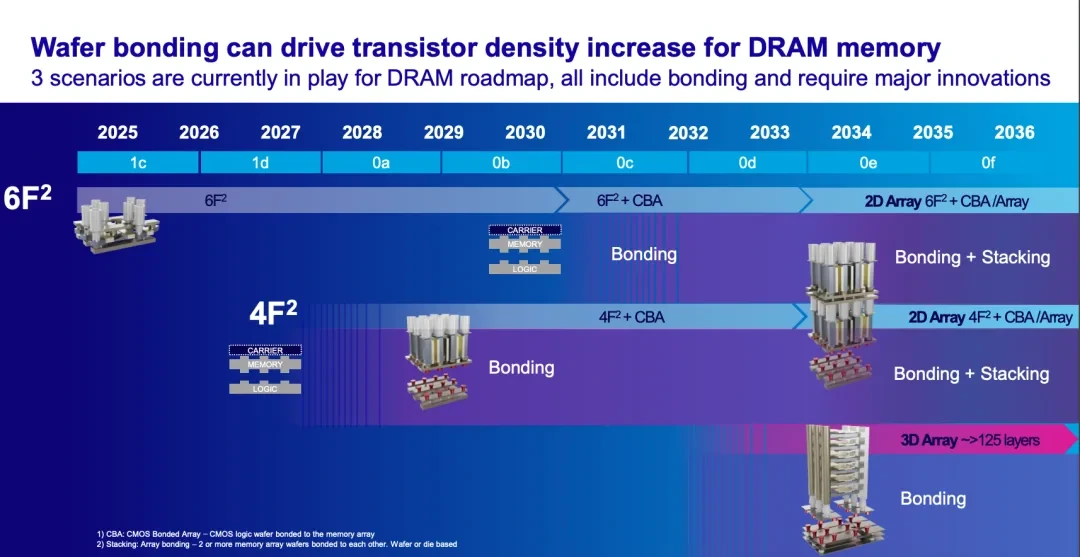

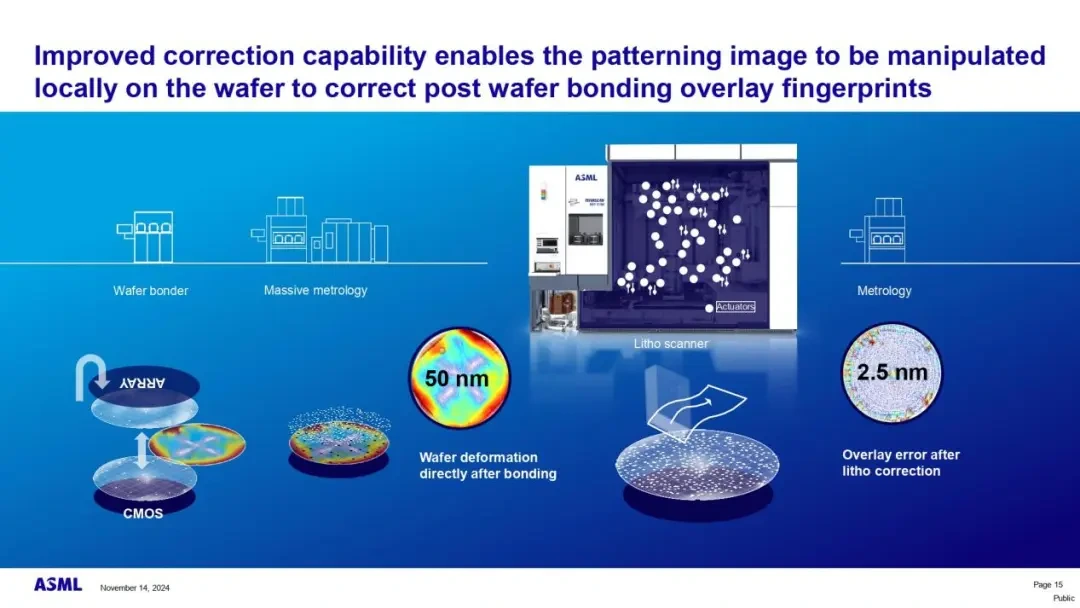

ASML은 또한 DRAM 메모리 트랜지스터의 밀도를 높일 수 있는 웨이퍼 본딩 기술의 잠재력을 지적합니다. 현재 DRAM 기술 로드맵에는 웨이퍼 본딩에 의존하고 상당한 혁신이 필요한 세 가지 시나리오가 있습니다. 아래 차트는 6F² 구조의 진행 상황을 보여주며 향후 몇 년(2025년, 2026년, 2027년) 동안의 개발 이정표를 보여줍니다. 2025년과 2026년에 표시된 D1c 노드, 2027년에 표시된 D1d 노드, 그리고 추가 6F² 구조입니다. 각 노드의 발전은 트랜지스터 밀도가 웨이퍼 본딩 기술에 의해 계속 증가할 것임을 나타냅니다.

6F² 아키텍처: 2025년 D1c 노드를 시작으로 6F² 아키텍처는 2025년부터 2030년까지 계속 발전할 것입니다. 2031년 이후에는 6F² + CBA(Cell-based Architecture) 단계에 진입하여 밀도를 더욱 높일 예정입니다. 6F² 아키텍처의 구현은 다층 오버레이에 의존하며 Carrier, Memory 및 Logic의 다층 본딩 구조를 채택합니다.

4F² 아키텍처: 2032년 이후에 구현될 것으로 예상되는 4F² 아키텍처도 CBA 아키텍처를 사용하며 더 복잡한 웨이퍼 본딩 기술에 의존합니다. 이 아키텍처는 DRAM 밀도를 더욱 높여 미래의 고성능 애플리케이션을 지원할 것입니다.

메모리 칩 기술 분야에서 기술 비용의 지속적인 절감은 고객의 의사 결정에 중요합니다. 기존 2D 어레이(6F²/4F²) 경로는 비교적 원활하며, CBA(CMOS Bonded Array) 본딩을 통해 비용을 점진적으로 최적화하여 2030년까지 허용 가능한 비용 범위 내에서 유지할 것입니다.

3D 어레이 개발 전망: 3D 어레이의 비용은 더욱 크게 감소하고 있지만 기술 및 제조 문제에도 직면해 있습니다. 현재의 3D 어레이 기술(5계층)은 성능과 비용 면에서 여전히 개선의 여지가 있습니다. 2032년까지 저장 밀도를 더욱 높이기 위해 3D 어레이에 125개 레이어의 새로운 설계가 도입될 것으로 예상됩니다. 그러나 이 노드를 실현하려면 새로운 DRAM 공장을 건설하고 많은 수의 새로운 장비를 투자해야 합니다.

소재 혁신의 가능성: 2032년 이후 추가적인 비용 절감 및 성능 향상은 새로운 소재의 적용에 따라 달라질 수 있으며, 이는 그래프의 녹색 점선으로 암시된 잠재적 경로입니다.

프로세스 통합: 3D 어레이가 점차 더 높은 레이어(예: 300개 레이어)를 달성함에 따라 "본딩 + 스태킹" 접근 방식을 채택하여 저장 밀도를 높이고 다단계 통합을 통해 비용을 최적화합니다.

EUV 리소그래피 개발

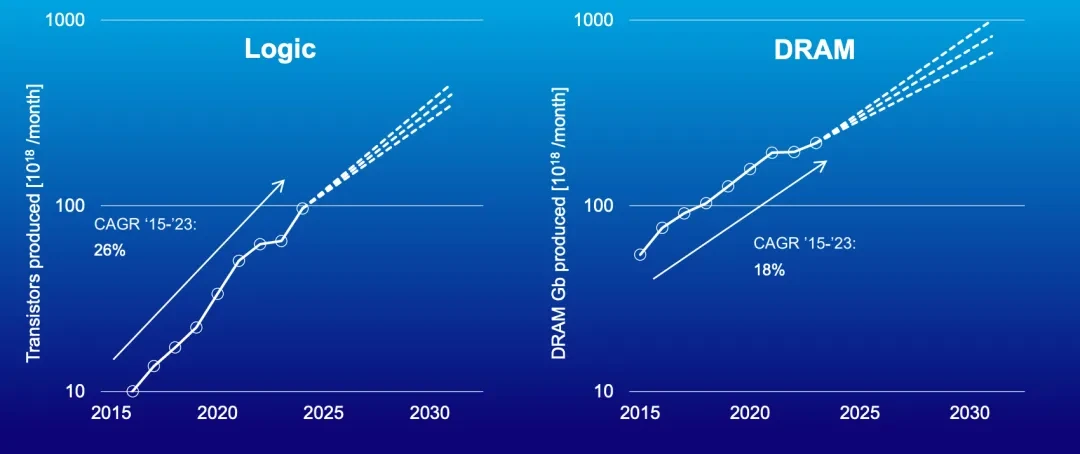

인공 지능 및 고성능 컴퓨팅에 대한 수요가 증가함에 따라 로직 칩 및 DRAM에 대한 생산 수요가 빠르게 증가하여 반도체 산업이 더 높은 성능과 더 높은 밀도의 방향으로 발전하고 있습니다. 2015년부터 2023년까지 로직 칩의 연평균 성장률(CAGR)은 26%에 달했으며 이러한 추세는 앞으로도 계속될 것으로 예상되며 더욱 가속화될 수 있습니다. DRAM은 2015년에서 2023년 사이에 18%의 CAGR로 성장했으며 앞으로도 이러한 강력한 상승 추세를 이어갈 것으로 예상됩니다.

출처: 로직 역사: ASML 최종 시장 모델, DRAM 기록: WSTS, 예측: ASML

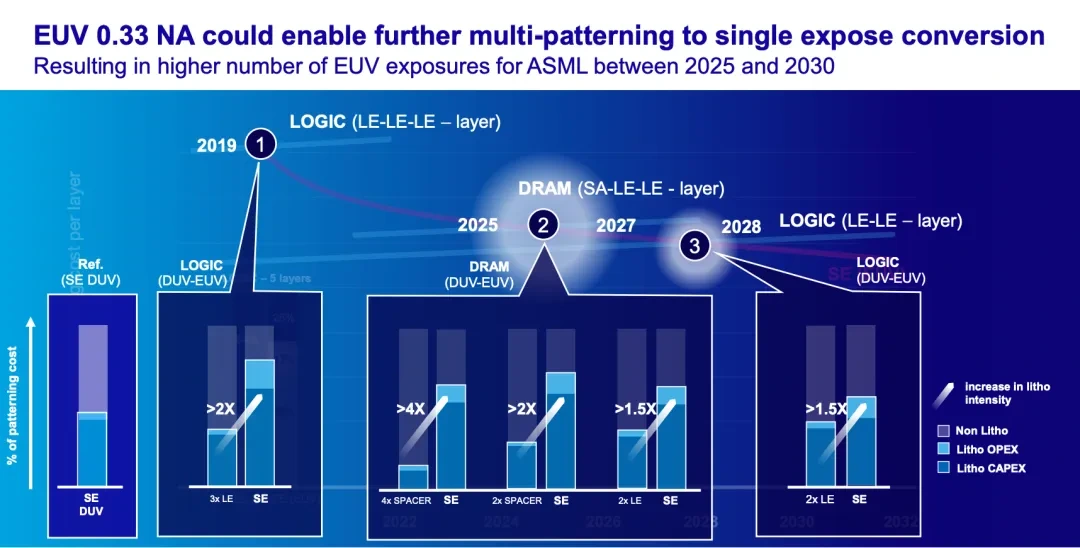

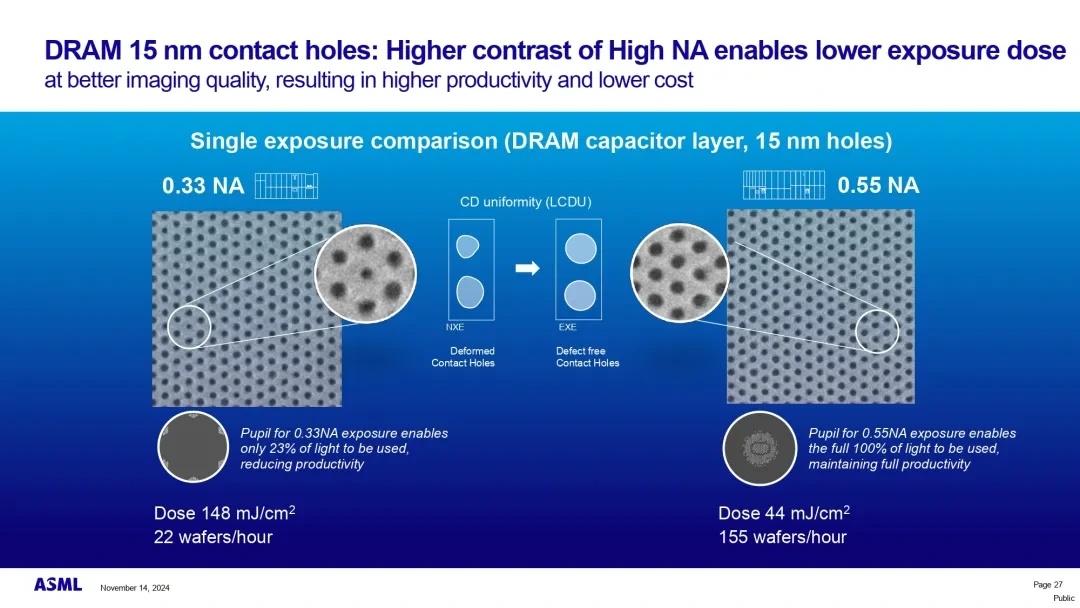

동시에 로직 칩과 DRAM은 주요 리소그래피 층의 성장을 더욱 주도할 것이며, 특히 EUV 0.33 NA 기술은 미래 노드에서 널리 사용될 것으로 예상됩니다. 기존의 다중 패턴 노광은 더 비싸고 다양한 층의 로직 칩 및 DRAM의 공정 요구 사항에 적합합니다. 그러나 EUV 0.33 NA의 점진적인 적용으로 단일 노광 비용은 점차 감소하고 있으며 점차 다중 패턴 노광 비용에 근접하고 낮아지고 있습니다.

EUV 0.33 NA는 단일 노광에 대한 다중 패턴을 더욱 가능하게 합니다.

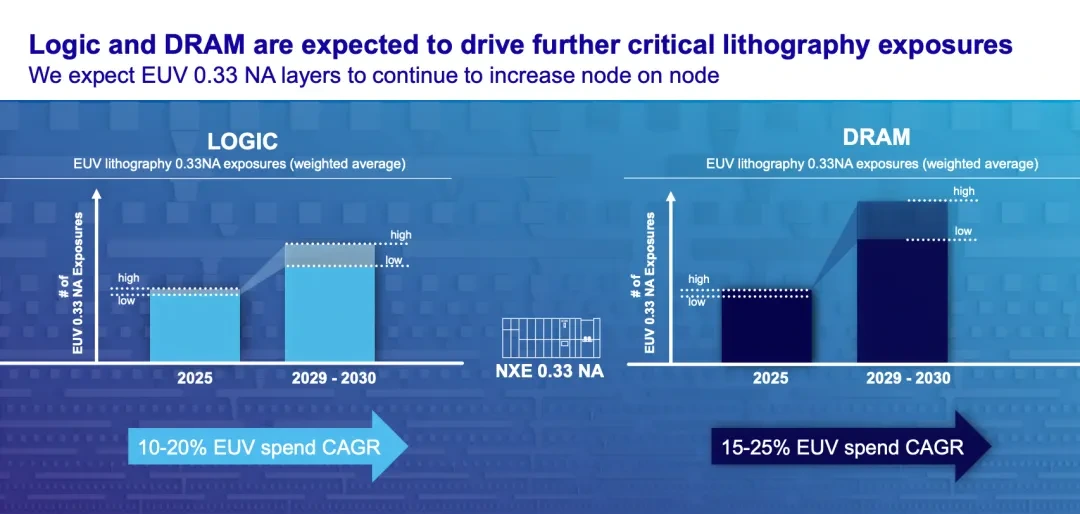

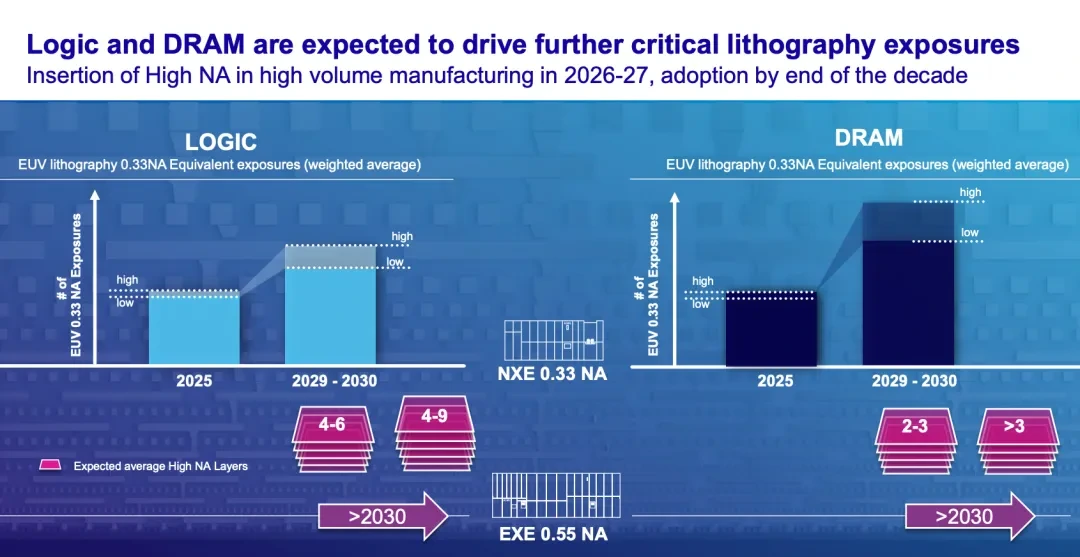

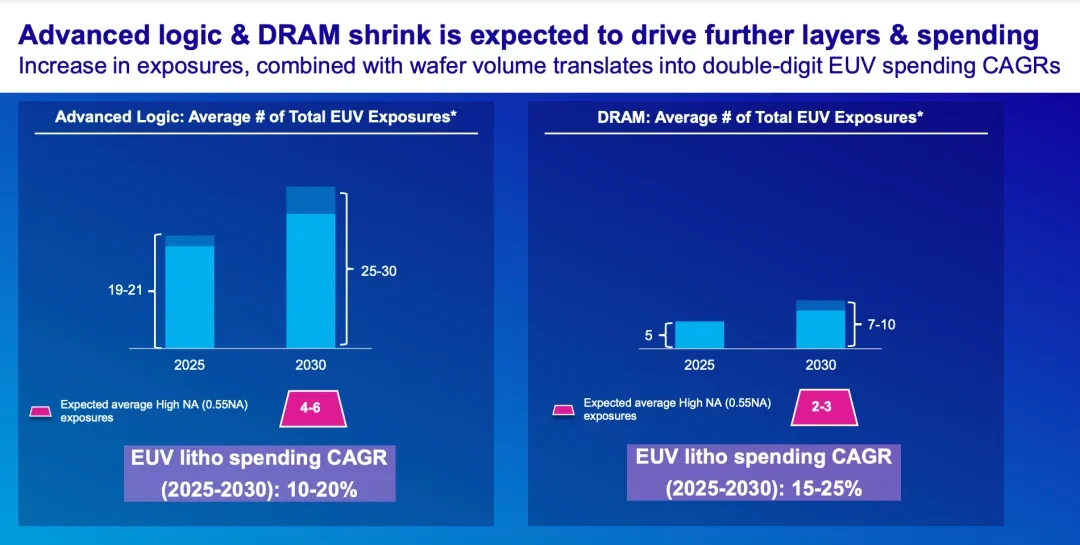

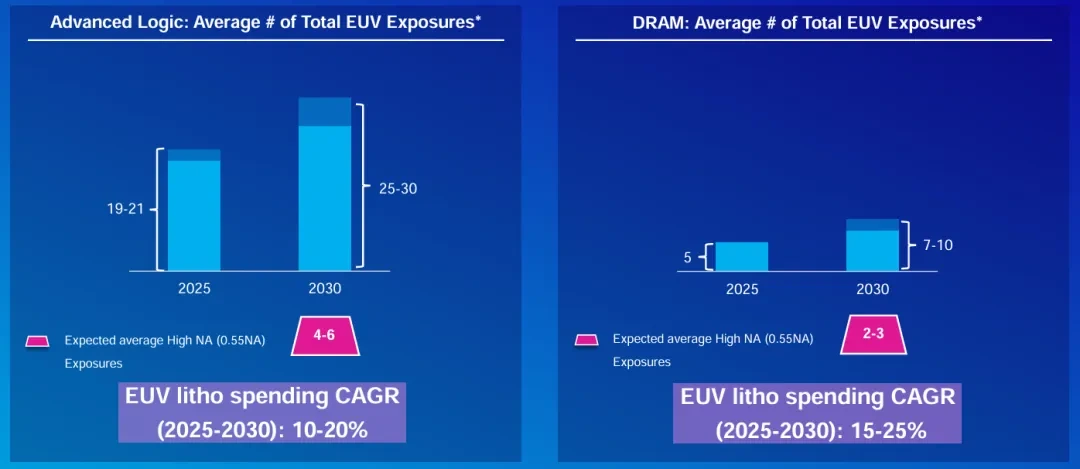

로직 칩과 D램은 0.33NA의 대형 노광 공정으로 제조될 예정이며, 아래 차트는 2025년에서 2030년 사이에 이 기술의 예상 사용을 보여줍니다. 로직 칩의 경우 EUV 0.33 NA에 사용되는 레이어 수는 2029-2030년까지 크게 증가할 것으로 예상되며, 이는 10-20%의 연평균 성장률(CAGR)에 해당합니다. 동시에 DRAM의 EUV 0.33NA 층은 더욱 크게 성장하고 있으며 이 기술에 대한 투자는 2029-2030년까지 15-25%의 CAGR로 성장할 것으로 예상됩니다.

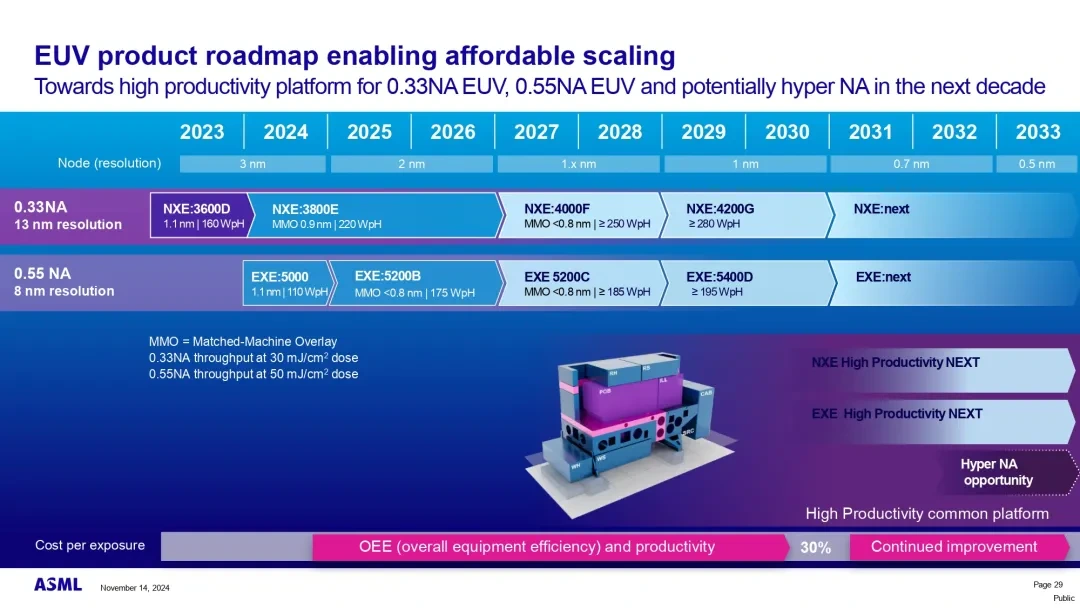

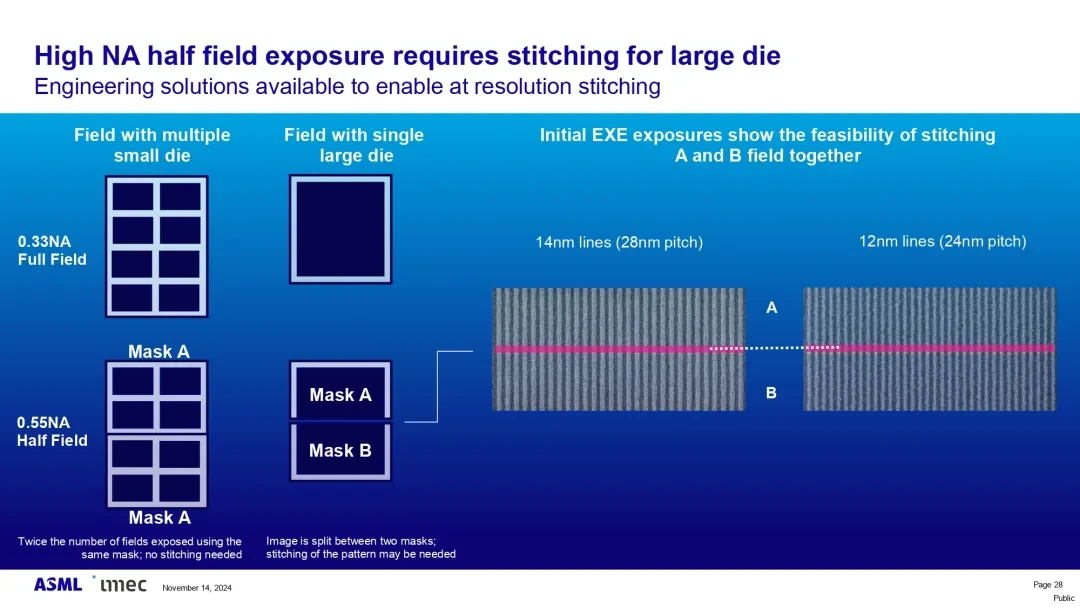

0.33 NA EUV가 26 nm보다 작은 금속 피치 가공을 위한 임계층으로 점진적으로 전환됨에 따라 0.55 NA EUV는 향후 더 높은 해상도와 효율적인 노광 공정을 가능하게 할 것으로 예상됩니다. 2025년경에는 0.55NA EUV 기술의 단일 노광이 대량 채택 시기에 접어들게 될 것이며, 21nm 메탈 피치에서 단일 노광에 대한 수요를 충족할 수 있을 것으로 예상되며, 다중 노광의 필요성은 해상도를 더욱 향상시킬 것입니다. 2030년 이후에는 16nm 이하의 노드에 0.55 NA EUV의 이중 노광 기술이 점진적으로 적용될 예정이다.

출처: 1Luc van den Hove, IMEC , ITF May 21, 2024

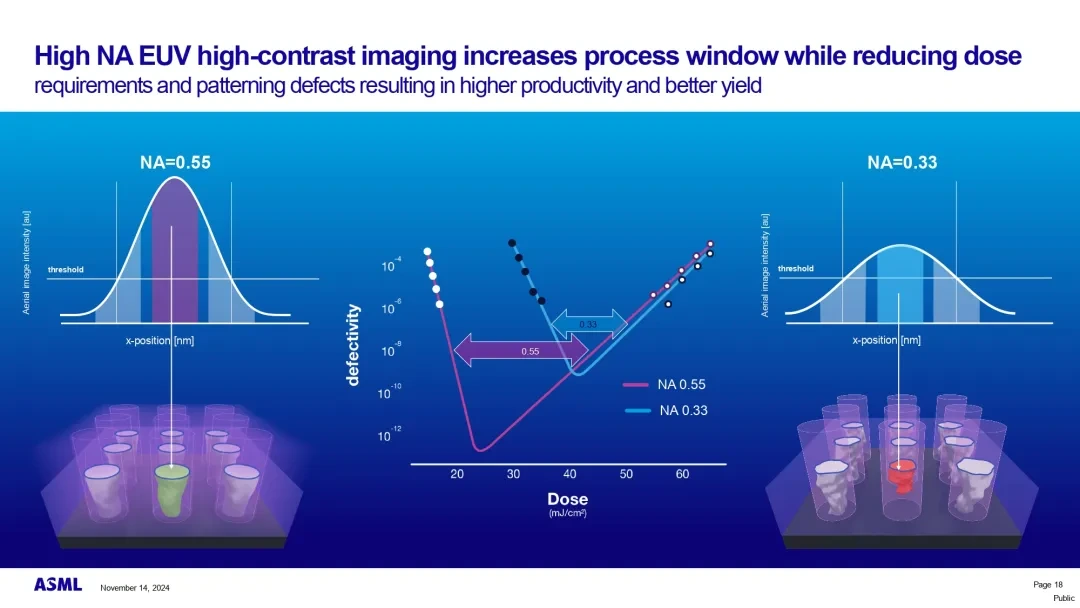

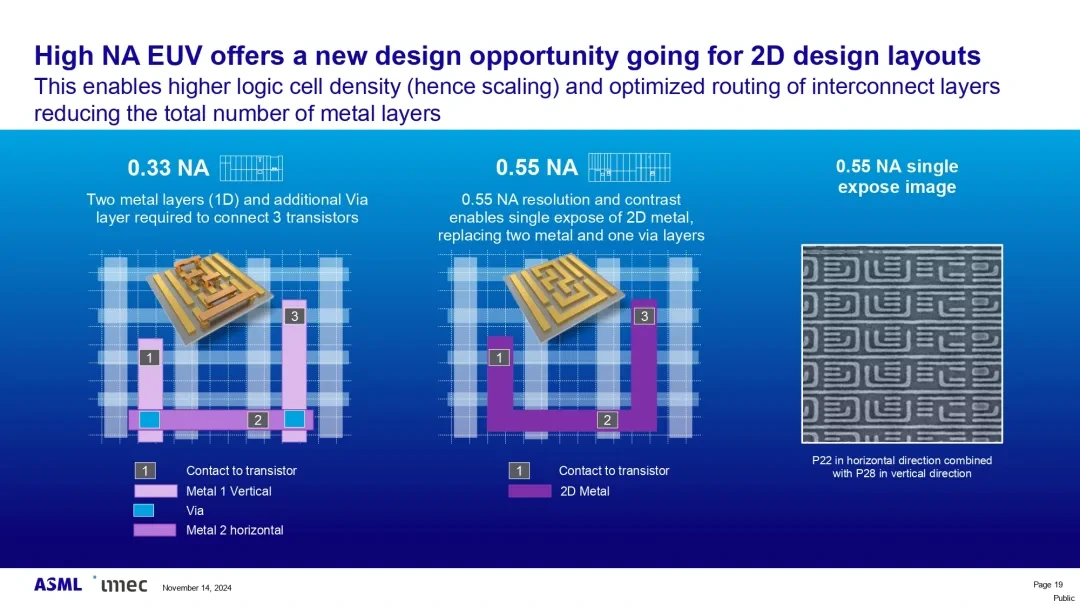

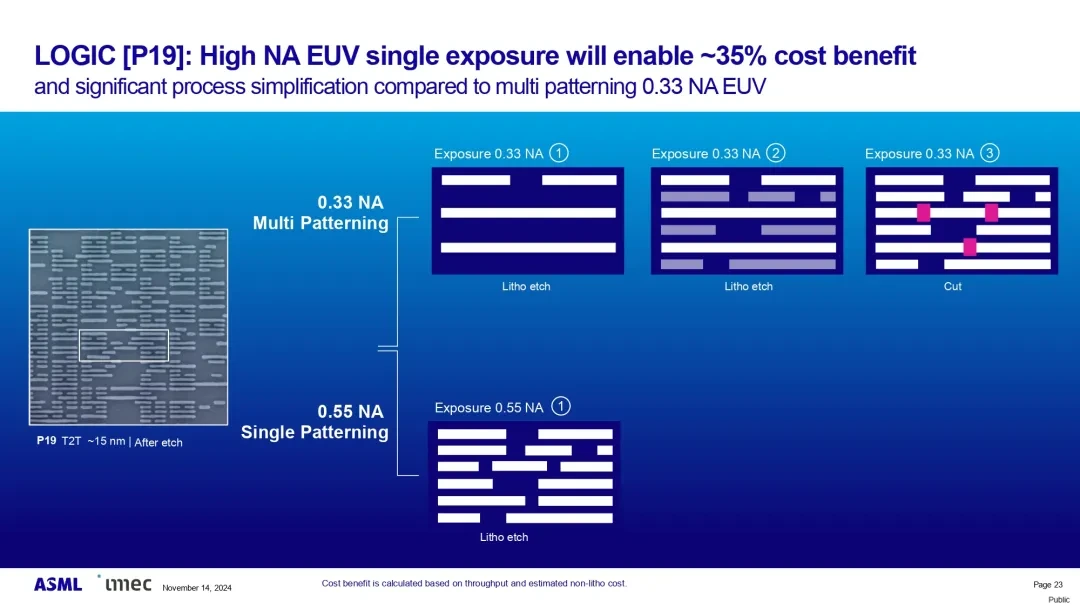

High NA(High Numerical Aperture) EUV 기술은 로직 칩의 1.5D 및 2D 설계에 더 큰 설계 자유도를 제공합니다. 높은 NA 단일 노광을 사용하면 공정 단계가 단순화되고 사이클 시간이 단축되며 낮은 NA 다중 패턴 노광에 비해 수율이 향상됩니다. 로직 칩의 금속층에 High NA 기술을 적용하면 약 35%의 비용 이점을 제공하는 동시에 공정 흐름을 크게 단순화할 것으로 예상됩니다.

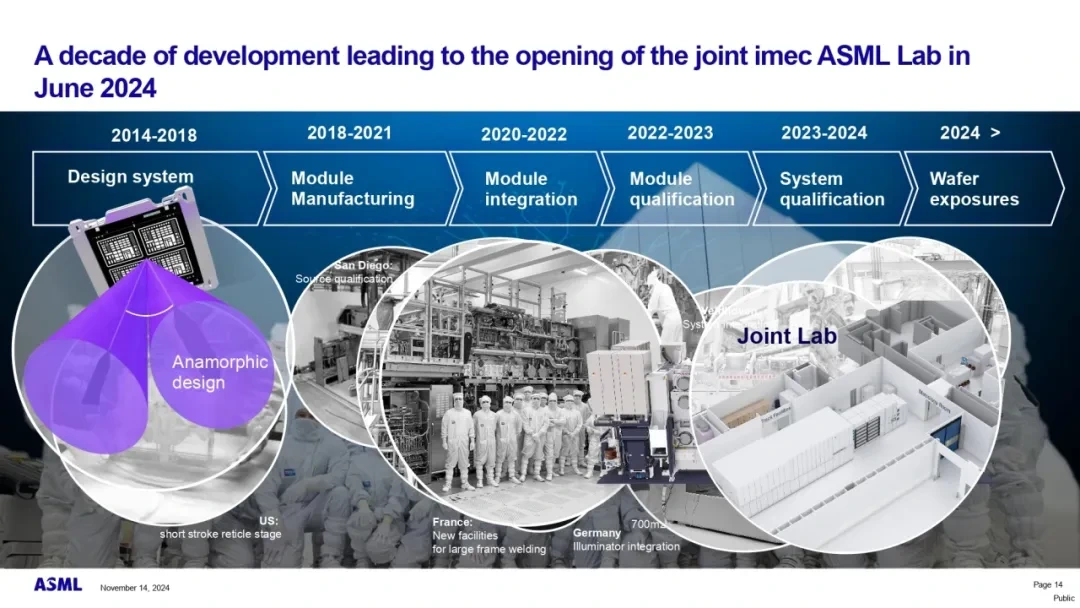

로직 및 DRAM은 핵심 리소그래피 기술, 특히 2026-2027년에 양산에 진입하고 2030년까지 널리 채택될 것으로 예상되는 High NA(High Numerical Aperture) EUV 기술의 개발을 더욱 주도할 것으로 예상됩니다. High NA(High Numerical Aperture) EUV 리소그래피의 최신 광학 혁신인 이 돌파구는 미래 EUV 기술 로드맵의 토대를 마련합니다. 비대칭 미러 설계 덕분에 EUV 시스템은 피코미터 안정성(실리콘 원자 직경의 1/200에 해당)을 달성하여 매우 높은 정확도를 보장합니다.

로직 칩의 경우, EUV 0.33 NA에 대한 노광 횟수는 2029년에서 2030년 사이에 크게 증가할 것으로 예상되며, 높은 NA에 대한 노광층 수도 2030년 이후 4-6개 또는 그 이상으로 증가할 것으로 예상됩니다. 이는 로직 칩 제조의 미래에는 더 높은 해상도와 밀도를 달성하기 위해 점점 더 많은 레이어가 높은 NA 기술을 필요로 할 것임을 의미합니다.

DRAM의 경우 EUV 0.33 NA의 노광층 수도 2029-2030년에 최고치를 경신할 것이며 2030년 이후에는 높은 NA 층의 수가 3개를 초과할 것입니다. 2030년 이후에는 EXE 0.55 NA 기술이 EUV 리소그래피의 적용 범위를 더욱 확장하고 더 높은 NA 층을 지원할 것으로 예상됩니다.

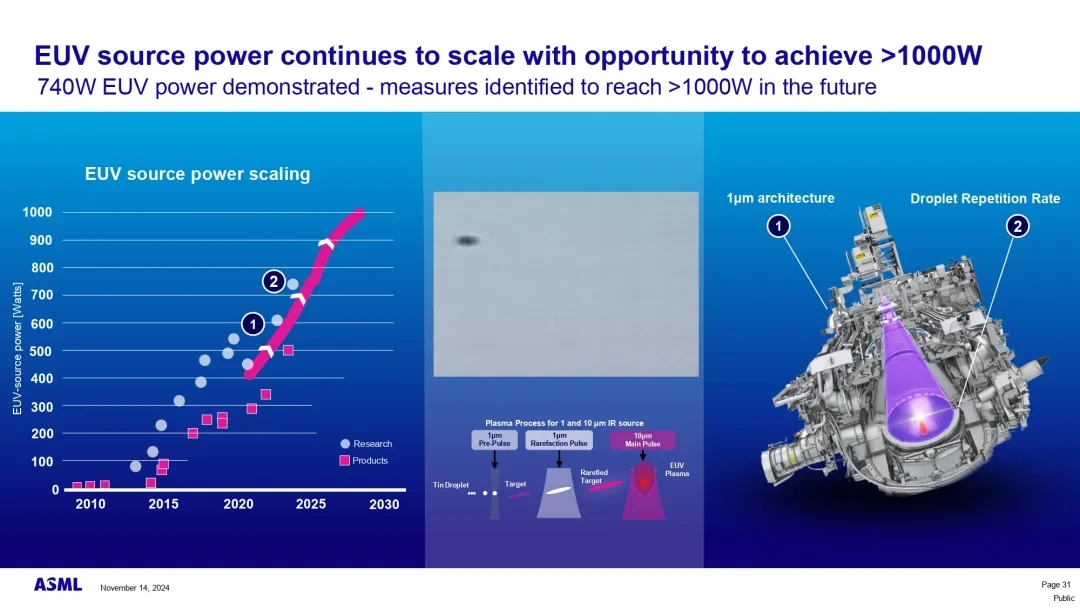

ASML는 또한 2010년 EUV 광원 전력이 100W 미만이었고, 현재 EUV 광원 전력은 740W에 도달했으며, ASML은 미래의 대량 제조의 요구를 충족시키기 위해 1000W 이상으로 더 증가하는 것을 목표로 하는 여러 기술적 조치를 확인했습니다.

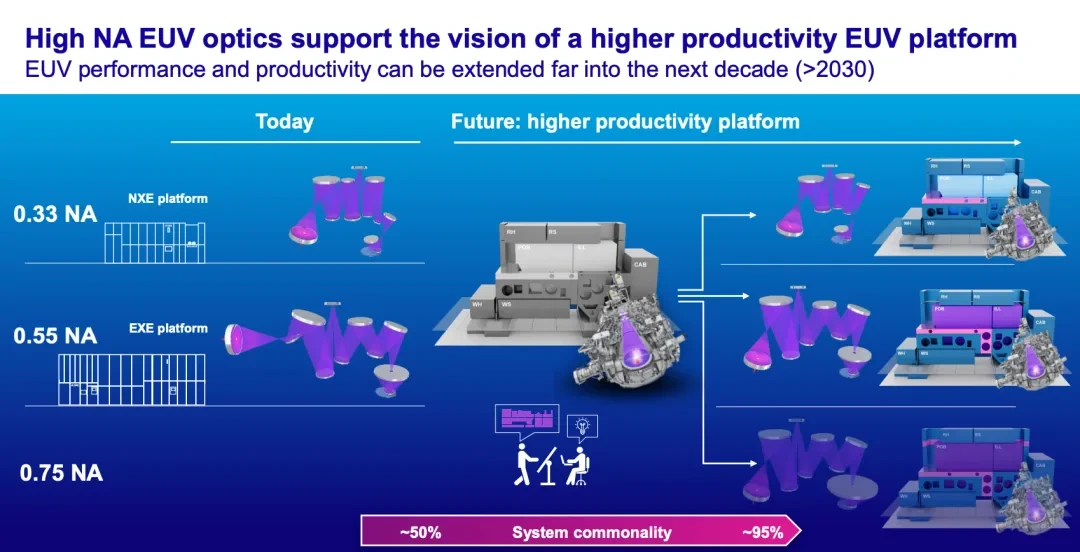

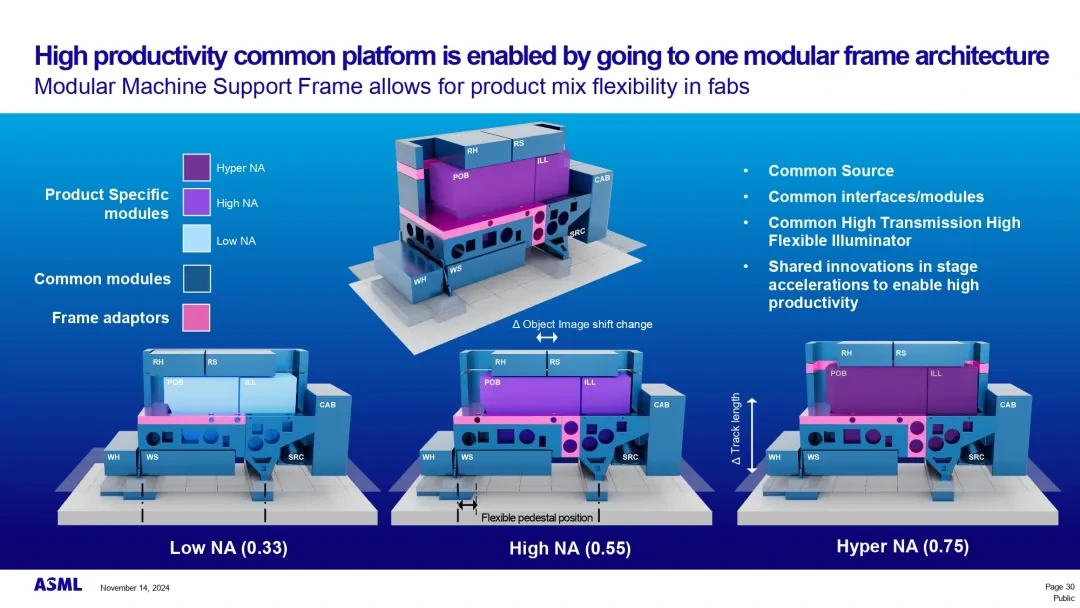

현재 EUV 플랫폼은 0.33 NA의 NXE 플랫폼과 0.55 NA의 EXE 플랫폼으로 나뉘어 있다. 이러한 플랫폼의 광학 시스템은 복잡하며 각 플랫폼의 시스템 공통성은 약 50%에 달하며, 이는 서로 다른 플랫폼 간에 공유되는 구성 요소의 수가 적다는 것을 의미하므로 시스템의 복잡성과 생산 비용이 증가합니다. 미래의 고생산성 EUV 플랫폼에는 0.75NA 광학 시스템을 도입하여 해상도와 정확도를 더욱 향상시킬 것입니다. 새로운 플랫폼의 설계는 플랫폼 간의 공통성을 크게 개선하여 최대 95%의 공통성을 기대할 수 있으며, 이는 대부분의 시스템 구성 요소를 서로 다른 NA 플랫폼에서 공유할 수 있음을 의미합니다. 이를 통해 제조 공정을 획기적으로 단순화하고 유지 보수 비용을 절감하며 장비 일관성과 호환성을 향상시킬 수 있습니다.

요약하면, 높은 NA 광학 혁신은 미래 EUV 플랫폼에 대한 견고한 기술 지원을 제공하여 고급 공정에서 보다 효율적인 리소그래피 작업을 가능하게 하여 향후 10년 동안 반도체 제조의 효율성과 경제성을 더욱 향상시킵니다.

로직 칩의 금속 간격이 16nm 이하로 떨어지는 2032년까지 0.75NA EUV 기술은 다중 패턴 0.55NA를 대체하는 효과적인 솔루션이 될 것으로 예상되며, 이를 통해 단일 노광 패터닝을 가능하게 하고 공정 복잡성을 줄이며 효율성을 개선할 수 있습니다. 2035년 이후에는 밀도 확장을 더욱 달성하기 위한 고급 노드 요구 사항을 수용하기 위해 0.75NA 다중 노출 공정을 채택할 수 있습니다.

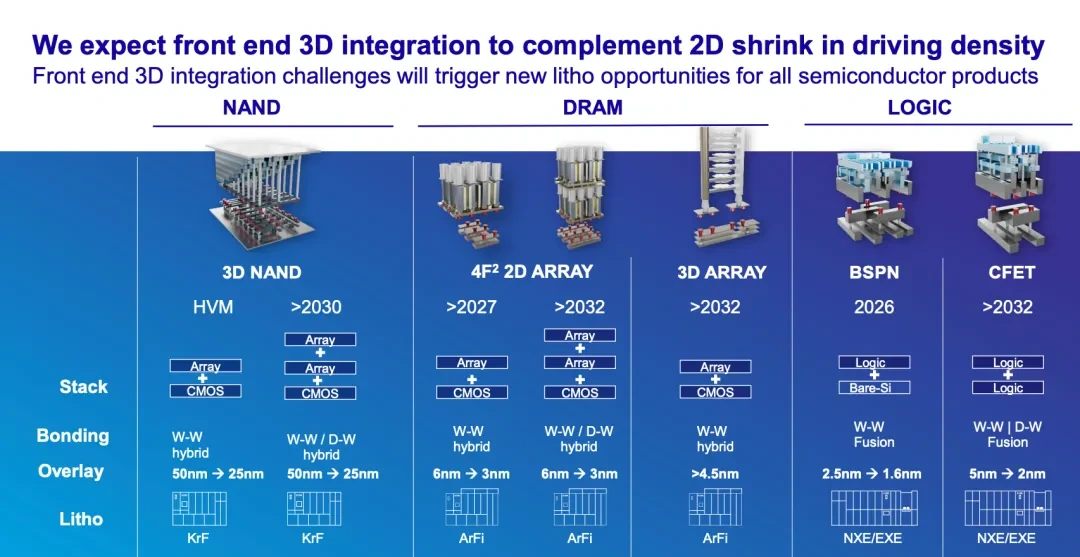

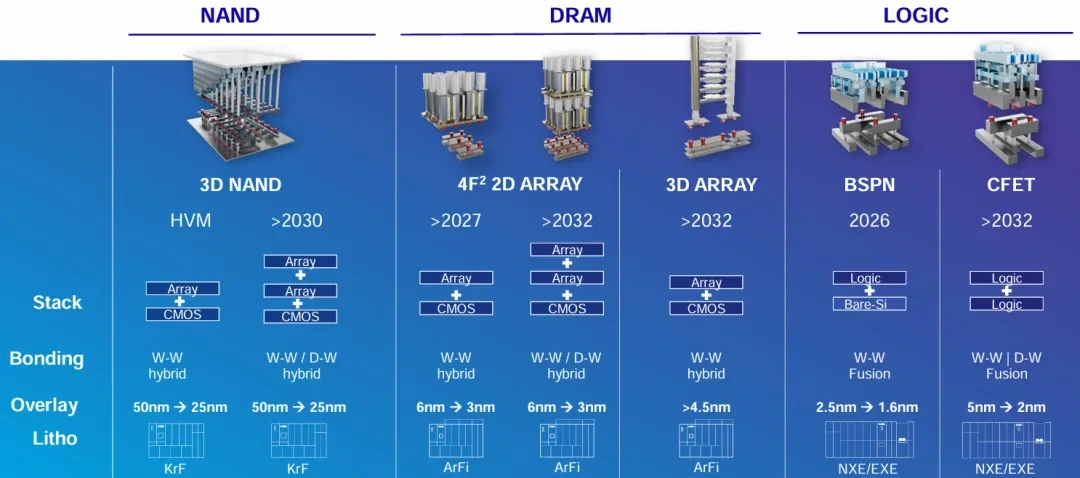

칩 밀도와 성능을 개선하기 위한 3D 및 2D와 같은 첨단 패키징 기술의 융합은 NAND, DRAM 및 로직 칩을 포함한 모든 반도체 제품에 새로운 리소그래피 기회를 열어줄 것입니다.

낸드: 3D 낸드는 2030년 이후 양산(HVM)에 들어갈 것으로 예상됩니다. 이 아키텍처에는 하이브리드 본딩 기술을 사용하여 50nm에서 25nm로 축소하는 CMOS 레이어가 있는 어레이 오버레이가 포함됩니다. 리소그래피 공정은 주로 KrF를 사용합니다.

DRAM: DRAM은 4F² 2D 어레이에서 3D 어레이로 진화할 것입니다. 4F² 2D 어레이는 2027년에 대량 생산에 도달할 것으로 예상되며, 2032년까지 3D 어레이 아키텍처로 전환할 것으로 예상됩니다. 3D 어레이 구조는 어레이와 CMOS 라미네이션, W-W 또는 D-W 하이브리드 본딩을 사용하고 피치는 6nm에서 3nm로 감소하며 리소그래피는 ArFi 공정을 사용합니다.

로직 칩: 로직 칩은 BSPN(2026) 및 CFET(2032년 이후) 아키텍처를 채택합니다. BSPN 구조는 로직과 베어 실리콘을 결합하고 본딩 피치를 2.5nm에서 1.6nm로 줄일 수 있으며 리소그래피 플랫폼은 NXE/EXE입니다. CFET 구조는 W-W 또는 D-W 하이브리드 본딩을 사용하는 로직 오버레이 로직 아키텍처를 사용하고 피치는 5nm에서 2nm로 감소하며 리소그래피는 NXE/EXE 플랫폼을 기반으로 합니다.

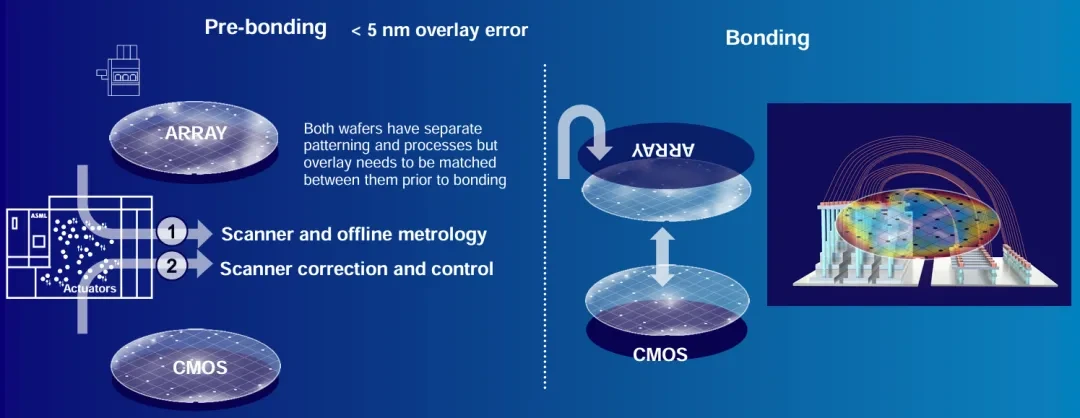

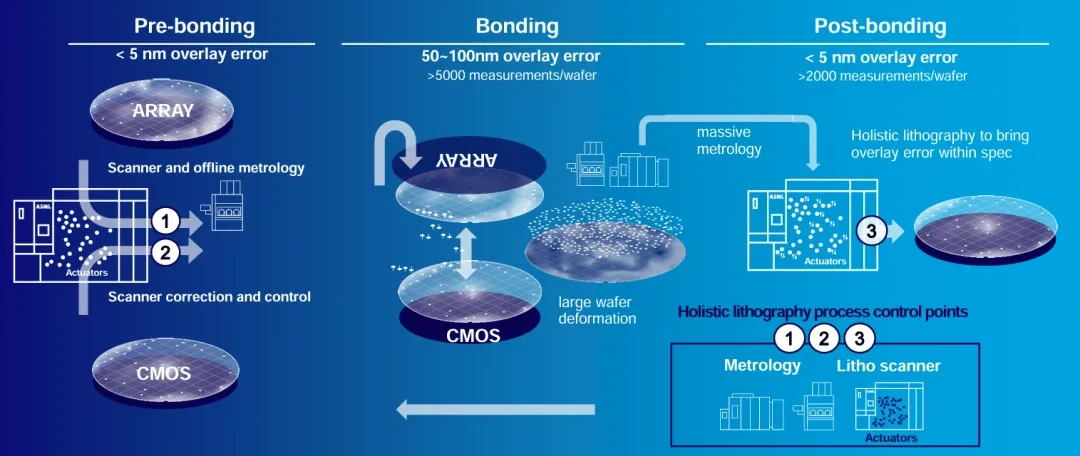

이러한 맥락에서 3D 통합에서 모놀리소그래피의 역할은 매우 중요하며, 모놀리소그래피는 사전 결합, 결합 및 사후 결합 단계에서 계측 및 스캔 제어를 통해 스택 업 정확도를 보장합니다. 이는 3D 구조에서 각 층의 정확한 중첩을 보장하여 고밀도 칩 제조를 강력하게 지원합니다.

ESG (환경경영)

향후 반도체 제조 공정의 최적화에서는 비용 및 에너지 소비 절감이 핵심 목표가 되어야 합니다. ASML은 웨이퍼 패터닝 공정의 전체 비용과 탄소 배출량을 줄이기 위한 세 가지 최적화 전략을 제안합니다.

- 공정의 각 단계에서 적격한 트랜지스터의 수를 늘려 생산 효율성을 높입니다.

- 전체 프로세스를 단순화하고 불필요한 단계를 줄이며 복잡성을 줄입니다.

- 각 처리 단계에서 비용과 배출량을 최소화하고 모든 단계에서 에너지 효율성을 최적화합니다.

아래 차트는 트랜지스터 밀도를 높이고 비용을 절감함으로써 지난 수십 년 동안 ASML이 이룬 성과를 보여주며, 이러한 추세는 향후 10년 동안 계속될 것으로 예상됩니다. 극자외선 리소그래피(EUV) 기술의 지속적인 개발로 ASML은 그래픽 정확도와 비용 효율성을 높였습니다. 이 그림은 EUV 0.33, EUV 0.55 및 향후 EUV 0.75를 포함한 다양한 세대의 EUV 기술의 적용을 보여주며, 기술 세대가 증가함에 따라 트랜지스터 밀도와 가격 대비 성능이 크게 향상됩니다. ASML은 EUV의 확장성을 확대하고 홀리스틱 리소그래피 솔루션을 채택함으로써 트랜지스터 밀도가 증가하는 역사적 추세를 2040년에도 이어받아 보다 발전된 반도체 공정을 지원할 것으로 예상된다고 밝혔다.

출처: ASML, 표준 셀 설계의 혁신 제외

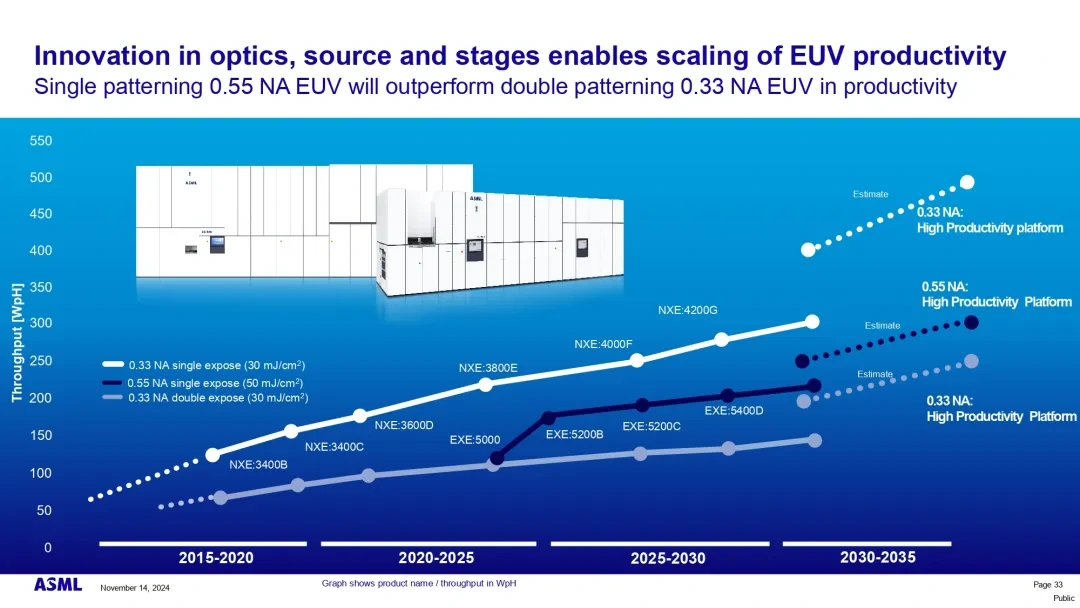

ASML의 EUV 혁신은 EUV의 에너지 소비를 크게 줄일 것으로 기대됩니다. 고객의 경우 웨이퍼당 필요한 에너지가 향후 15년 동안 80% 감소할 것으로 예상됩니다. 이 그래프는 시간당 웨이퍼 처리량(WPH), 총 전력 및 웨이퍼당 에너지 소비의 개선 추세를 보여줍니다. 기술의 발전으로 웨이퍼당 에너지 소비는 급격히 감소했으며 웨이퍼 처리량은 해마다 증가했지만 총 전력 소비는 비교적 안정적인 수준을 유지했습니다. 이는 EUV 기술이 단위 에너지 소비를 크게 줄이면서 효율성을 향상시킨다는 것을 보여줍니다.

ASML의 목표는 2050년까지 지구 온도 상승을 1.5°C로 제한함으로써 사회가 지속 가능성 약속을 이행할 수 있도록 돕는 것입니다.

최종 시장, 웨이퍼 수요 및 리소그래피 지출

반도체 산업의 장기 전망은 여전히 긍정적이며, 미션 크리티컬 반도체는 여러 주요 트렌드에 의해 주도되는 시장에서 중요한 역할을 하고 있습니다. 특히 인공지능의 부상은 업계에 상당한 기회를 제시하고 있으며, 글로벌 반도체 매출은 2025년에서 2030년 사이에 연평균 9%의 성장률로 성장하고 2030년까지 1조 달러를 초과할 것으로 예상됩니다.

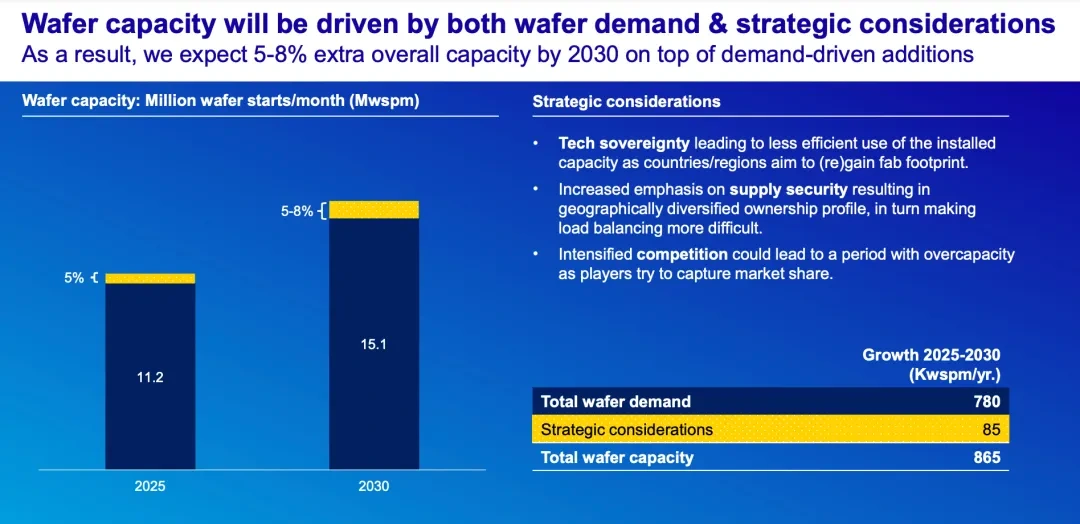

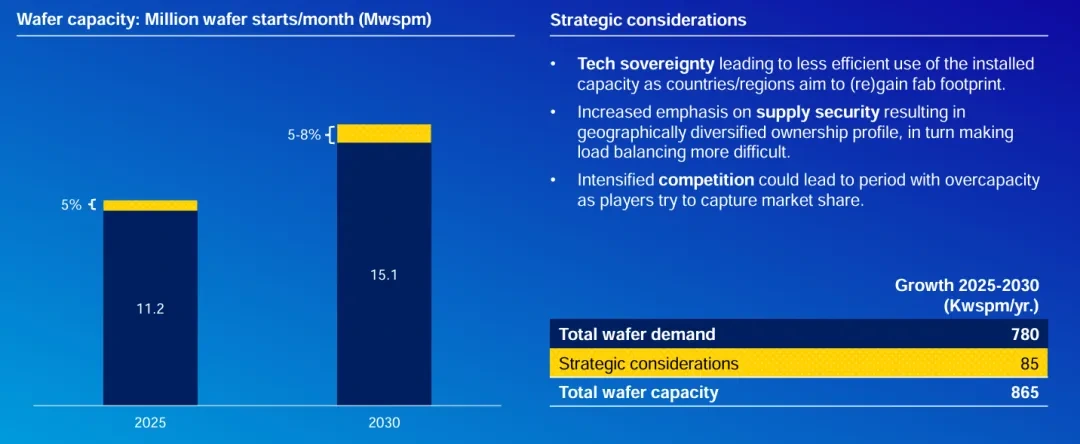

이러한 최종 시장 전망은 연간 780,000개의 웨이퍼에 대한 전체 수요 증가(2025-2030년)로 해석되며, 주요 최종 동인인 AI도 리소그래피 지출에서 웨이퍼 수요 구조의 긍정적인 변화를 주도하고 있습니다. 전체 웨이퍼 용량은 수요 주도 성장을 충족하고 전략적 확장을 고려하기 위해 2030년까지 추가로 5-8% 증가할 것으로 예상됩니다.

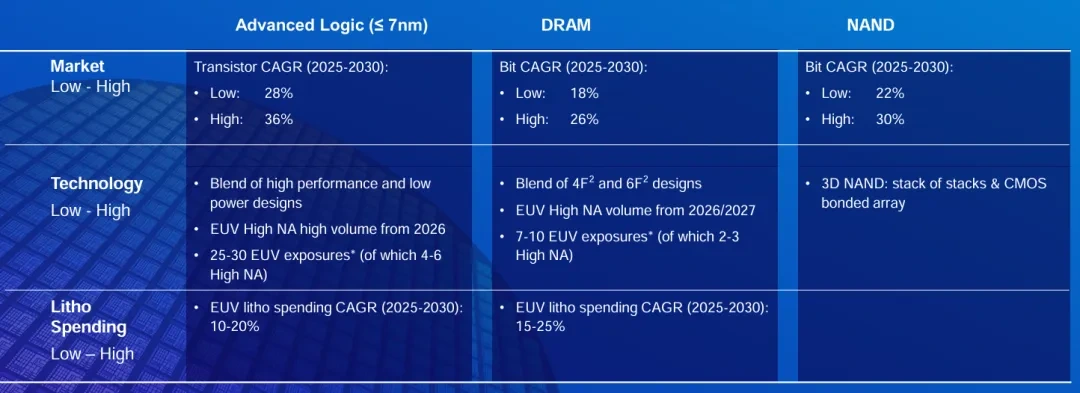

첨단 로직 및 DRAM 측면에서, 추가적인 확장은 EUV 리소그래피 층과 지출의 증가를 주도할 것입니다. 첨단 로직의 경우, 높은 개구수(0.55NA) 층을 가진 EUV 리소그래피 지출은 2025년에서 2030년 사이에 연평균 10-20%의 성장률로 증가할 것으로 예상됩니다. DRAM 분야에서는 낮은 개구수(0.33NA) 및 높은 개구수(0.55NA) 층의 증가로 EUV 리소그래피 지출이 연평균 15-25%의 성장률을 기록할 것으로 예상됩니다.

ASML의 장기 기회 모델은 시장의 힘, 기술 선택 및 전략적 고려 사항의 조합에 의해 주도됩니다. 이 모델은 "최종 시장"에서 시작하여 다양한 산업의 수요 변화를 분석하고 이를 웨이퍼 수요로 변환하여 높음, 중간 및 낮음 시나리오를 사용하여 수요 규모를 예측합니다. 그런 다음 웨이퍼 수요는 리소그래피 장비에 대한 글로벌 투자 수요로 변환되고 ASML의 시장 점유율이 추정됩니다. 동시에 기존 장비의 관리를 고려하여 설치 기반의 비즈니스 성장을 추정하고 2030년까지의 시장 시나리오를 최종적으로 도출하여 높음, 중간 및 낮음의 다양한 시나리오를 지원합니다. 이 체계적인 분석 프레임워크는 ASML이 전략을 더 잘 개발하고 시장 기회를 포착하는 데 도움이 됩니다.

최종 시장

반도체는 연결된 세계, 기후 변화 및 자원 부족, 사회 및 경제적 변화와 같은 여러 영역에서 필수 불가결한 역할을 하며 여러 사회 개발 메가트렌드의 핵심 조력자로서 반도체 산업에 대한 장기 전망은 여전히 긍정적입니다.

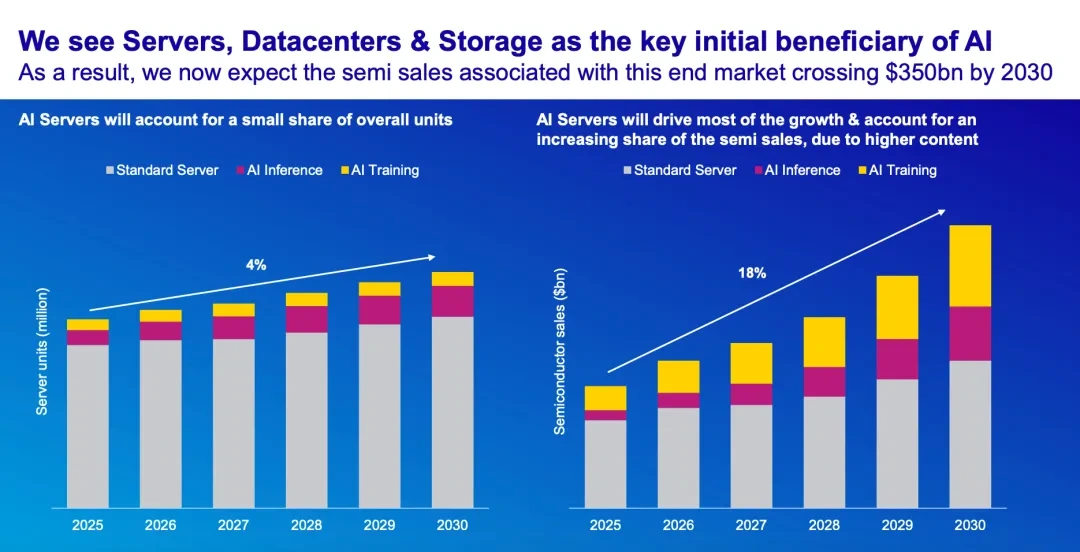

AI에 힘입어 서버, 데이터센터, 스토리지 부문은 반도체 시장의 주요 수혜자가 될 것이며, 이 시장의 반도체 매출은 2030년까지 3,500억 달러를 초과할 것으로 예상됩니다.

서버 단위: 2025년부터 2030년까지 AI 서버(AI 추론 및 AI 학습 서버 포함)는 전체 서버 수에서 상대적으로 적은 비율을 차지하지만 수치에서 점차 증가할 것입니다. AI 서버는 전체 서버 시장의 4%를 차지할 것으로 예상됩니다.

반도체 판매: AI 서버는 서버 단위의 수보다 반도체 판매 성장에 더 중요한 역할을 할 것입니다. AI 서버 콘텐츠에 대한 수요가 증가함에 따라 반도체 매출에서 AI 서버가 차지하는 비중은 계속 증가할 것입니다. 차트에 따르면 시장은 18%의 연평균 성장률(CAGR)로 성장하고 있으며 반도체 판매에 대한 AI 서버의 기여도는 2030년까지 크게 증가할 것입니다.

출처: ASML 분석

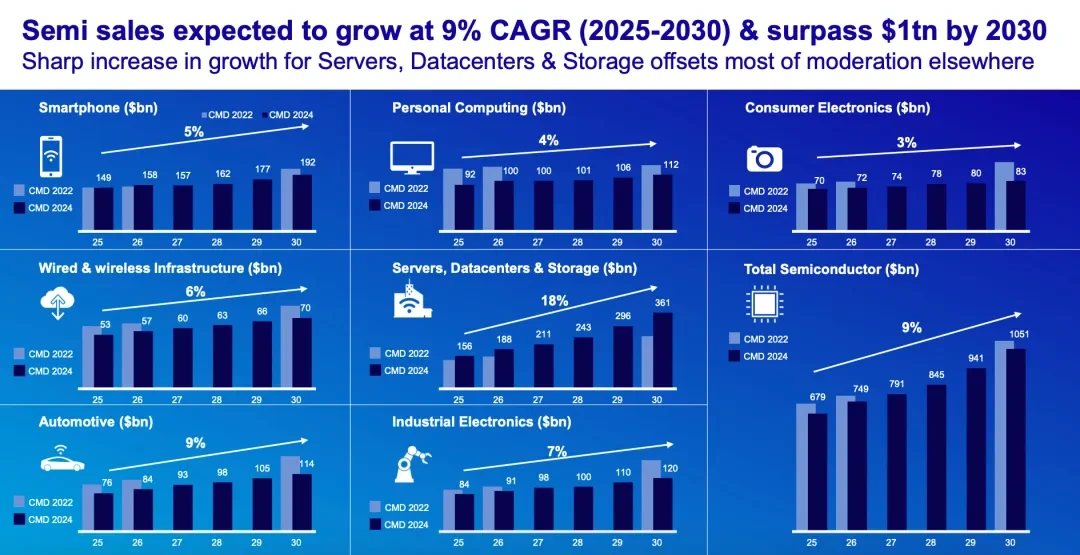

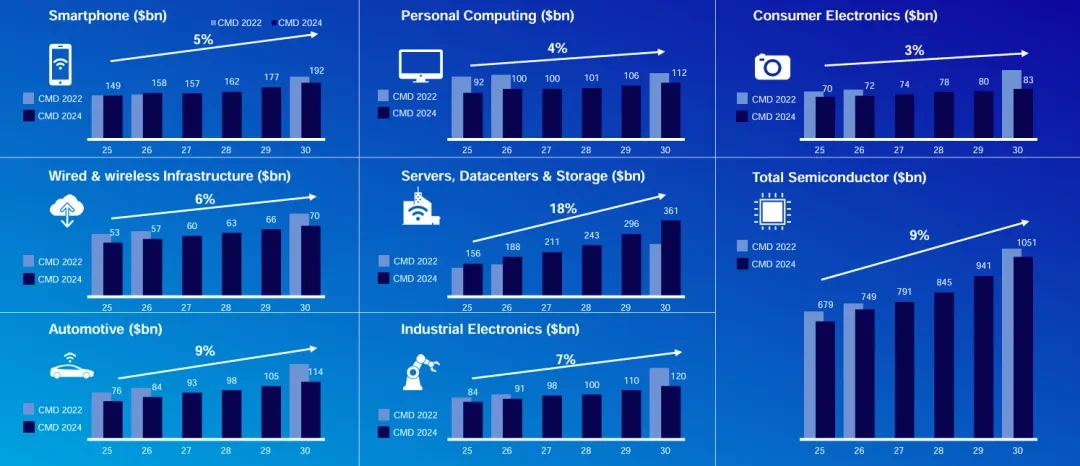

반도체 매출은 2025년에서 2030년 사이에 9%의 연평균 성장률(CAGR)로 성장하여 2030년까지 총 1조 달러 이상으로 성장할 것으로 예상됩니다. 세그먼트별 성장은 다음과 같습니다.

출처: ASML 분석

- 스마트폰: 2025년 1,490억 달러에서 2030년 1,920억 달러로 5%의 꾸준히 성장할 것으로 예상됩니다.

- 개인 계산: 2030년까지 1,120억 달러에 이를 것으로 4%의 성장률을 보이며, 이는 소비자 수요의 꾸준한 증가를 반영합니다.

- 소비자 가전: 연평균 성장률이 3%로 둔화되고 있으며 2030년까지 830억 달러에 이를 것으로 예상됩니다.

- 유선 및 무선 인프라: 2030년까지 6% 성장하여 700억 달러에 이를 것으로 예상됩니다.

- 서버, 데이터 센터 및 스토리지: 이 부문은 AI 성장의 혜택을 받고 있으며 2030년까지 18%의 CAGR로 성장하여 3,610억 달러에 이를 것으로 예상되어 가장 빠르게 성장하는 부문이 될 것으로 예상됩니다.

- 자동차: 연평균 9%의 성장률로 2030년까지 1,140억 달러에 이를 것으로 예상됩니다.

- 산업용 전자 제품: 성장률은 7%이며 2030년까지 1,200억 달러에 이를 것으로 예상됩니다.

전반적으로 반도체 시장의 성장은 주로 서버, 데이터 센터 및 스토리지에 대한 수요 급증에 의해 주도되며, 이는 다른 영역의 완만한 성장을 보상하여 반도체 산업을 높은 성장 추세로 유지할 것입니다.

웨이퍼 수요

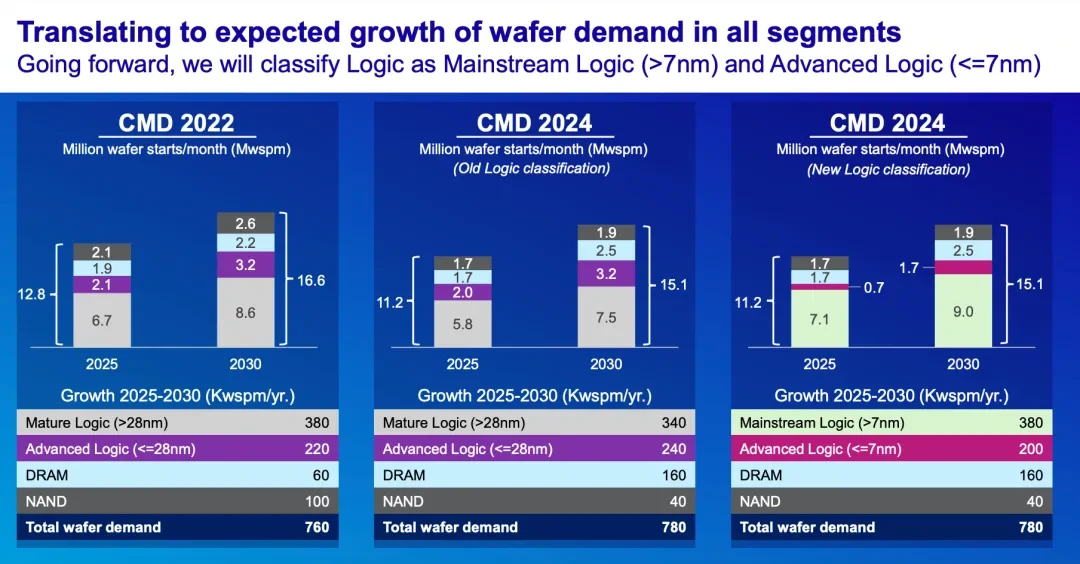

아래 차트는 다양한 반도체 부문에서 향후 몇 년 동안 예상되는 웨이퍼 수요 증가를 보여주는 동시에 새로운 논리적 분류 방법론을 명확히 합니다.

CMD 2022년 예측: 글로벌 월간 웨이퍼 수요는 2025년까지 1,280만 개의 웨이퍼(Mwspm)에 도달하고 2030년까지 1,660만 개의 웨이퍼로 더욱 증가할 것으로 예상됩니다. 주요 성장은 성숙한 로직(> 28nm)과 고급 로직(≤ 28nm)에 대한 수요가 주도했으며, 각각 670만 개와 860만 개로 증가했습니다. 그 중 성숙한 로직, 고급 로직, DRAM 및 NAND 수요의 증가는 각각 380, 220, 60 및 100 Kwsmp/년이며 총 수요 증가는 760 Kwsmp/년입니다.

CMD 2024에 대한 이전 분류 예측: 웨이퍼 수요는 기존 논리적 분류 방법론에 따라 2025년 1,120만 개에서 2030년 1,510만 개로 증가할 것으로 예상됩니다. 이전 분류에서 수요 증가는 성숙한 논리(580만 개에서 750만 개)와 고급 논리(2.0에서 320만 개)에 집중되었습니다. 전체 수요 증가에는 Mature Logic 340, Advanced Logic 240, DRAM 160 및 NAND 40 Kwsmp/year가 포함되며 총 780 Kwsmp/year입니다.

CMD 2024에 대한 새로운 분류 예측: 웨이퍼 수요는 로직을 주류 로직>7nm)과 고급 로직≤7nm)으로 나누는 새로운 로직 분류 방법을 사용하여 2025년 1,120만 개에서 2030년 1,510만 개로 증가할 것으로 예상됩니다. 주류 로직과 고급 로직에 대한 수요는 각각 710만 개와 900만 개에 달했습니다. 새로운 로직 분류에 따라 주류 로직의 성장은 380Kwsmp/년, 고급 로직은 200Kwsmp/년, DRAM은 160Kwsmp/년, NAND는 40Kwsmp/년, 총 수요 증가는 780Kwsmp/년으로 예상됩니다.

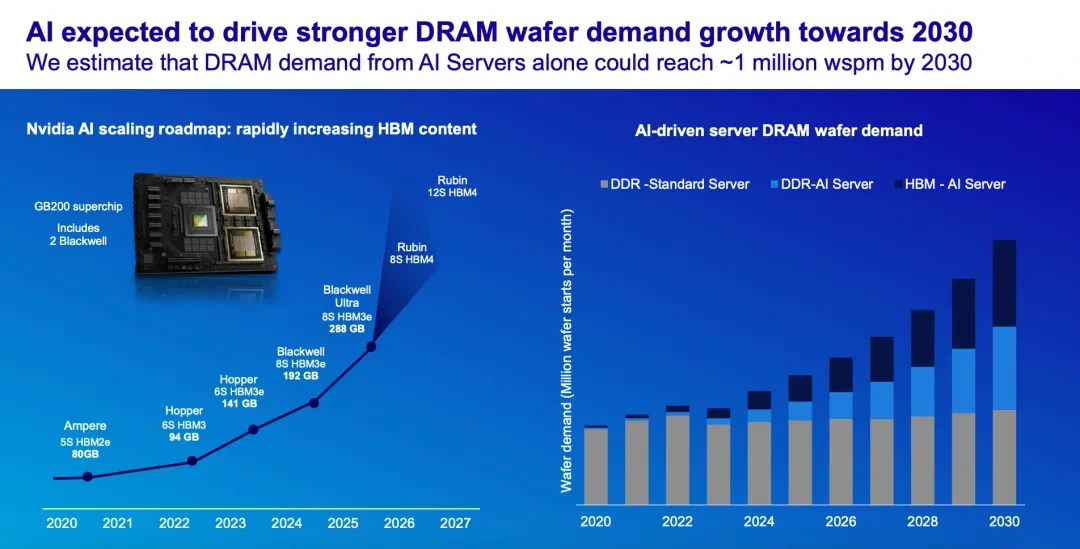

AI의 급속한 발전으로 고성능 메모리에 대한 수요가 크게 증가하여 2030년까지 DRAM 시장의 성장을 크게 주도할 것으로 예상됩니다. 엔비디아의 AI 칩은 2020년부터 암페어 칩의 HBM2e(80GB) 칩 5개에서 2027년 예상되는 HBM4 칩 12개로 HBM의 구성을 점진적으로 늘려 AI 칩의 고성능 메모리 수요가 크게 증가했음을 보여준다. 또한 AI 기반 서버는 DRAM 웨이퍼에 대한 수요를 주도하고 있으며, 이로 인해 2030년까지 DRAM 웨이퍼 수요가 월 약 100만 개에 이를 것으로 예상됩니다.

웨이퍼 수요는 첨단 로직, DRAM 및 NAND 시장의 건전한 성장으로 인해 2025년에서 2030년까지 향후 몇 년 동안 증가할 것으로 예상됩니다. 구체적으로, 첨단 로직을 위한 트랜지스터의 수는 2025년 대비 2030년까지 32% 증가할 것으로 예상됩니다. 2030년까지 DRAM 비트 성장률은 22%로 예상됩니다. 낸드비트 성장률은 2030년까지 26%에 이를 것으로 예상됩니다.

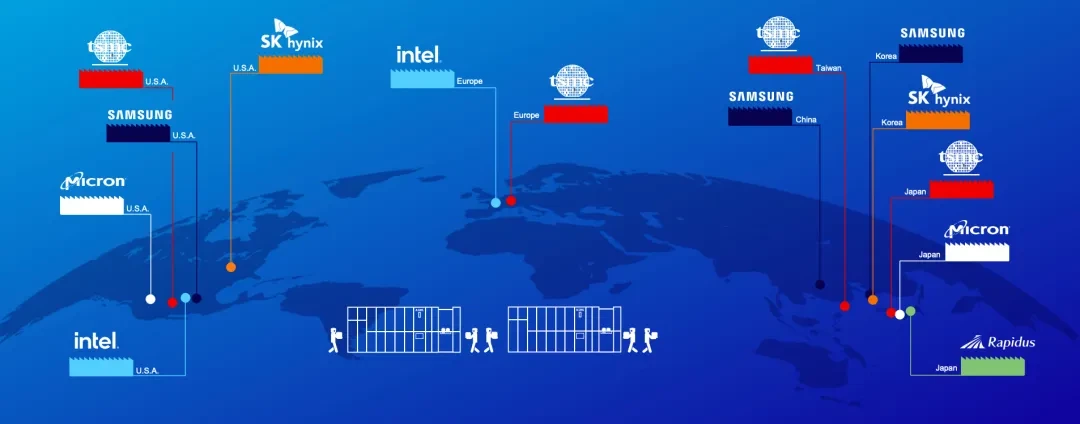

미국의 520억 달러 규모의 반도체법(CHIPS Act), 유럽의 반도체법(European CHIPS Act) 도입, 인도의 '인도 반도체 미션(Indian Semiconductor Mission)'을 통한 100억 달러 정부 투자, 일본의 반도체 개발 전략 수립을 위한 260억 달러의 투자 및 세액 공제 약속 등 세계 여러 국가 및 지역에서 현지 웨이퍼 제조 능력을 향상시키기 위해 취한 전략적 이니셔티브

웨이퍼 팹 건설과 관련하여, 미주에 18개의 새로운 웨이퍼 팹이 건설될 것으로 예상되며, 유럽/중동에 12개의 새로운 웨이퍼 팹이 건설될 것으로 예상되며, 아시아에 78개의 새로운 웨이퍼 팹이 건설될 것으로 예상되며, 이는 아시아가 여전히 글로벌 반도체 제조의 주요 지역이 될 것임을 시사합니다. 주요 웨이퍼 제조업체로는 TSMC, 삼성, 인텔 등이 있습니다. TSMC는 미국, 유럽, 대만 및 기타 지역에 투자합니다. 삼성전자는 미국, 중국, 한국에 새로운 공장을 설립합니다. SK하이닉스, 미국과 한국에서 생산 능력 확대 Micron은 또한 미국과 일본에 공장을 두고 있습니다. 미국에 투자하는 것 외에도 Intel은 유럽에서도 확장하고 있습니다. 일본 스타트업 래피더스(Rapidus)도 일본에 본사를 두고 있다.

출처: 공시, ASML 분석

글로벌 웨이퍼 생산 능력은 수요 주도 성장에 힘입어 2030년까지 총 용량의 5-8%까지 증가할 것으로 예상됩니다. 웨이퍼 수요는 2025년부터 2030년까지 연간 780Kwsmp로 증가할 것으로 예상되며, 전략적 고려 사항에 따라 추가 85Kwsmp/년 용량 증가로 총 용량은 865Kwsmp/년으로 증가할 것으로 예상됩니다. 이는 주로 다음과 같은 전략적 고려 사항을 기반으로 합니다: 1) 기술 주권: 국가와 지역이 팹에 대한 통제권을 (재)획득하기를 원함에 따라 기존 용량은 덜 효율적으로 사용됩니다. 2) 공급 보안: 공급 보안에 대한 강조로 인해 지리적으로 다각화된 팹 소유자 레이아웃이 등장했지만 이로 인해 로드 밸런싱의 어려움도 증가했습니다. 3) 경쟁 심화: 시장 점유율을 놓고 경쟁하는 기업은 과잉 생산 능력으로 이어질 수 있습니다.

출처: ASML 분석

리소그래피 지출

2030년까지 첨단 로직 및 DRAM의 감소는 EUV 노광층의 수 증가와 EUV 지출 증가를 더욱 주도할 것으로 예상됩니다.

출처: ASML 분석

첨단 로직에 힘입어 2025년 평균 총 EUV 노출은 19-21세이며 2030년까지 25-30세로 증가할 것으로 예상됩니다. 높은 개구수(0.55NA)에서 예상되는 평균 노출 횟수는 4-6으로 증가합니다. EUV 리소그래피 지출은 10-20%(2025-2030)의 연평균 성장률(CAGR)로 증가하고 있습니다.

DRAM에 대한 수요에 힘입어 2025년 평균 총 EUV 익스포저는 5회가 될 것으로 예상되며, 2030년에는 7-10회로 증가할 것으로 예상됩니다. 높은 개구수(0.55NA)에서 예상되는 평균 노출 횟수는 2-3으로 증가합니다. EUV 리소그래피 지출 CAGR은 15-25%(2025-2030년)입니다.

EUV 제품 및 비즈니스 기회

반도체 제조에서 EUV(Extreme Ultraviolet Lithography) 기술은 뛰어난 정밀도와 효율성으로 산업의 미래를 선도하고 있습니다. EUV 기술의 선두 주자인 ASML은 최근 EUV 기술의 성숙도, 혁신, 글로벌 가용성 및 생산량, 향후 시장 전망에 대해 자세히 설명했습니다.

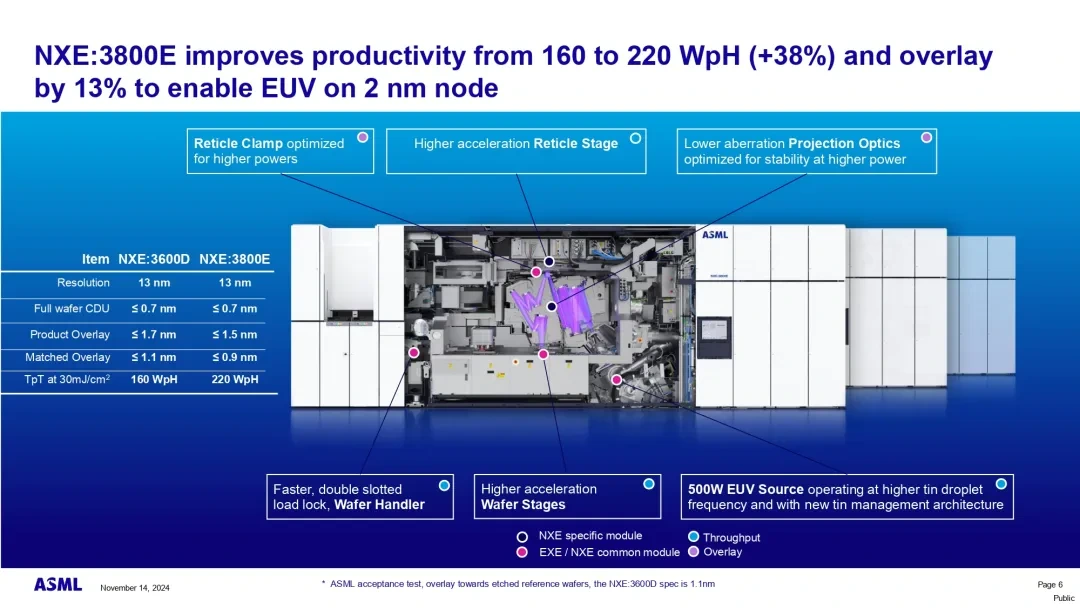

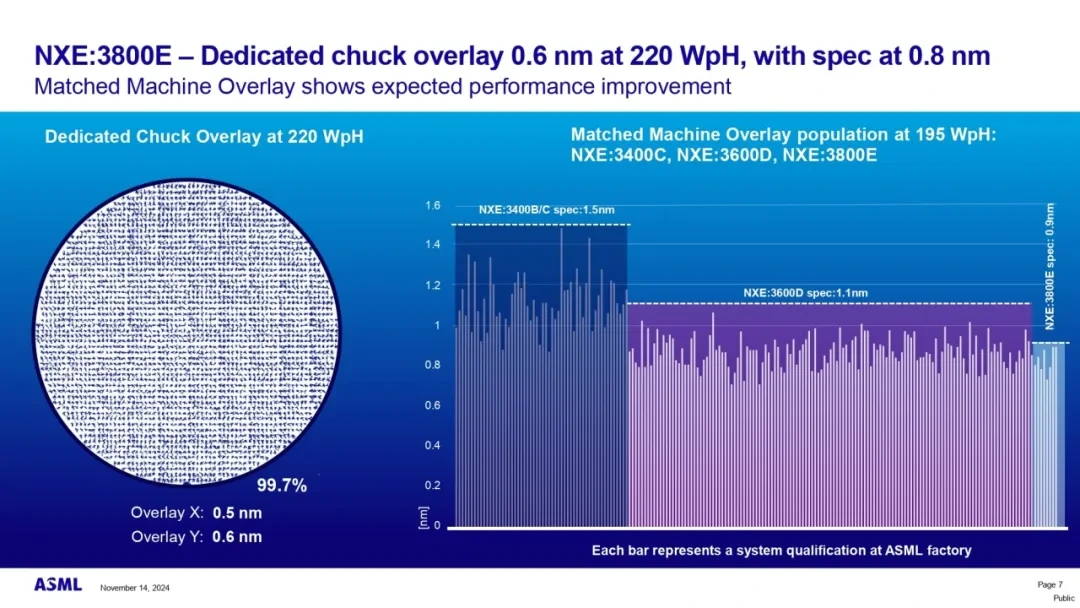

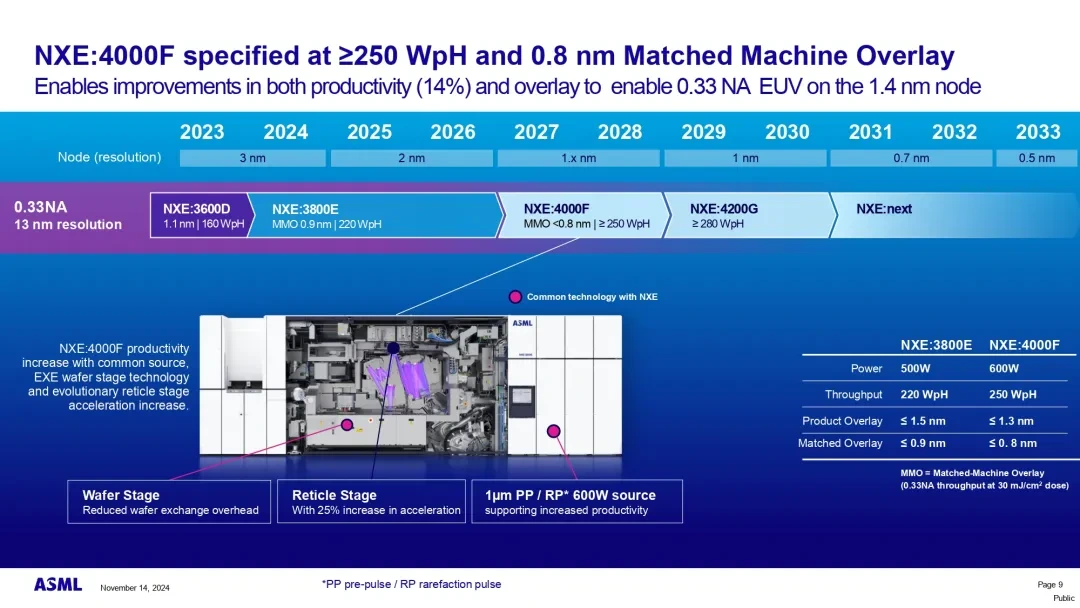

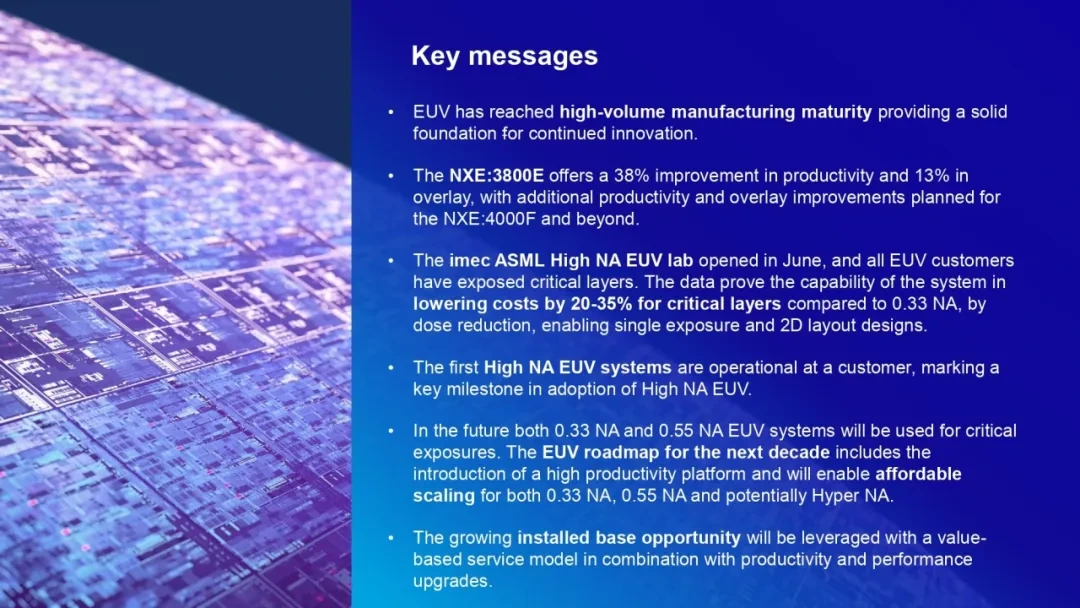

ASML은 EUV 기술이 대량 생산의 성숙 단계에 진입해 지속적인 혁신을 위한 견고한 기반을 제공한다고 밝혔다. 그 중 NXE:3800E 시스템은 생산성과 커버리지가 각각 38%와 13% 증가하여 크게 개선되었습니다. 이러한 발전은 EUV 기술 분야에서 ASML의 선도적 입지를 강화할 뿐만 아니라 향후 기술 업그레이드 및 확장을 위한 견고한 기반을 마련합니다.

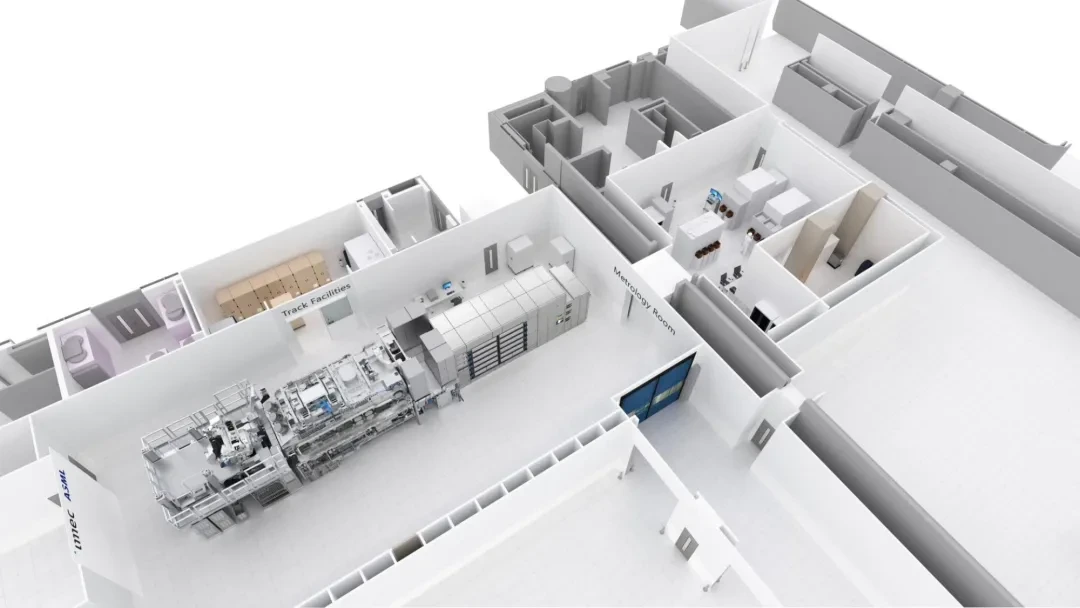

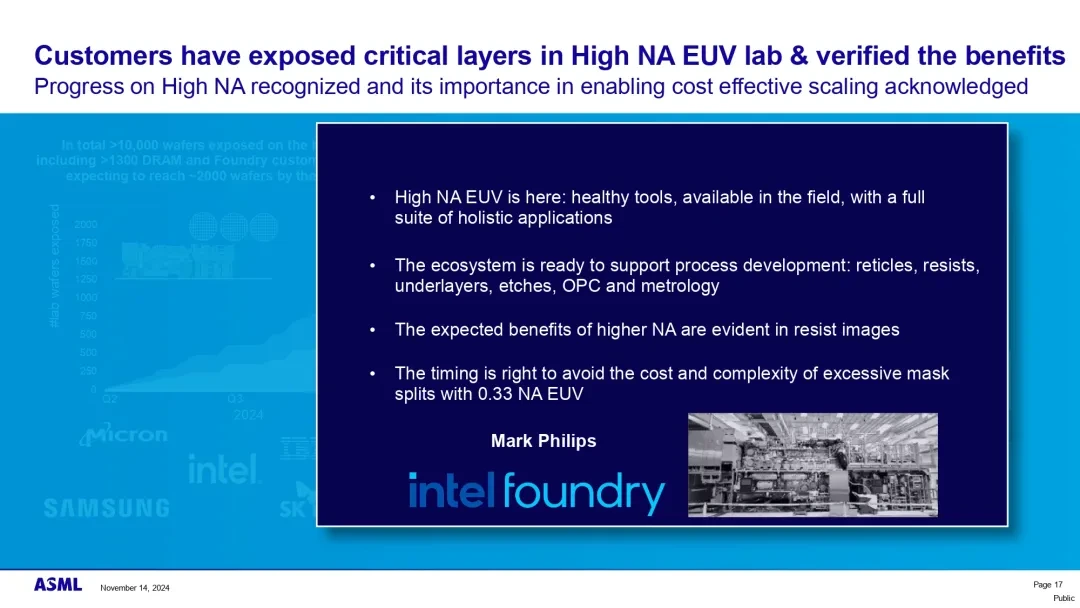

특히 imec ASML의 High NA EUV Lab 설립은 EUV 기술의 새로운 발걸음을 내디뎠습니다. 이 연구소는 올해 6월에 공식 문을 열었으며, 모든 EUV 고객이 주요 계층에 노출되었습니다. 실험 데이터는 단일 노출 및 2D 레이아웃 설계를 달성하기 위해 선량을 줄여 생산 비용을 크게 절감함으로써 임계 층의 비용을 줄이는 데 있어 높은 NA EUV 시스템의 상당한 이점을 완전히 보여줍니다.

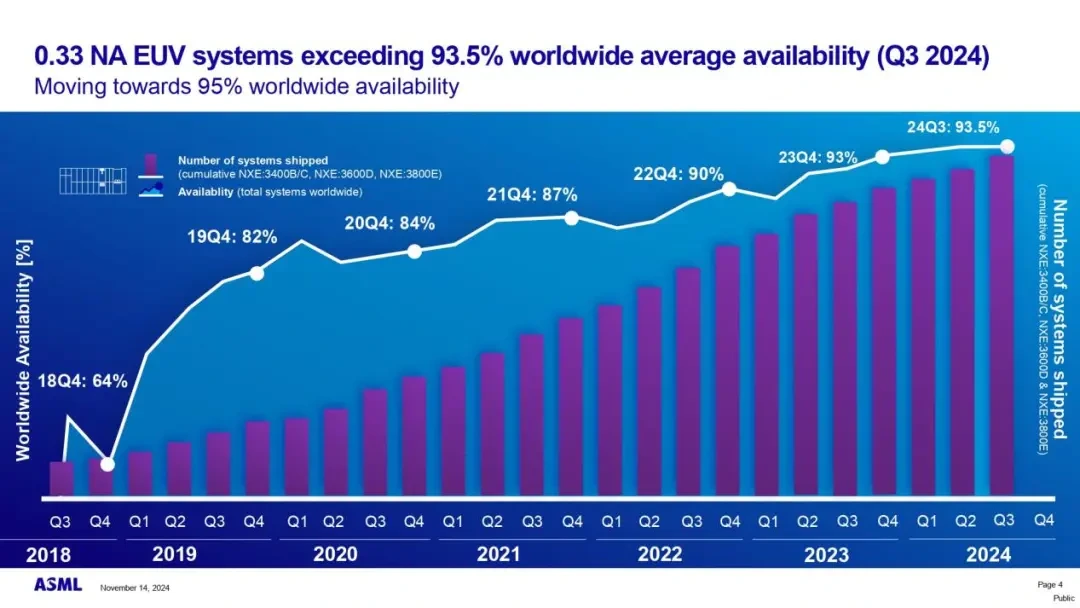

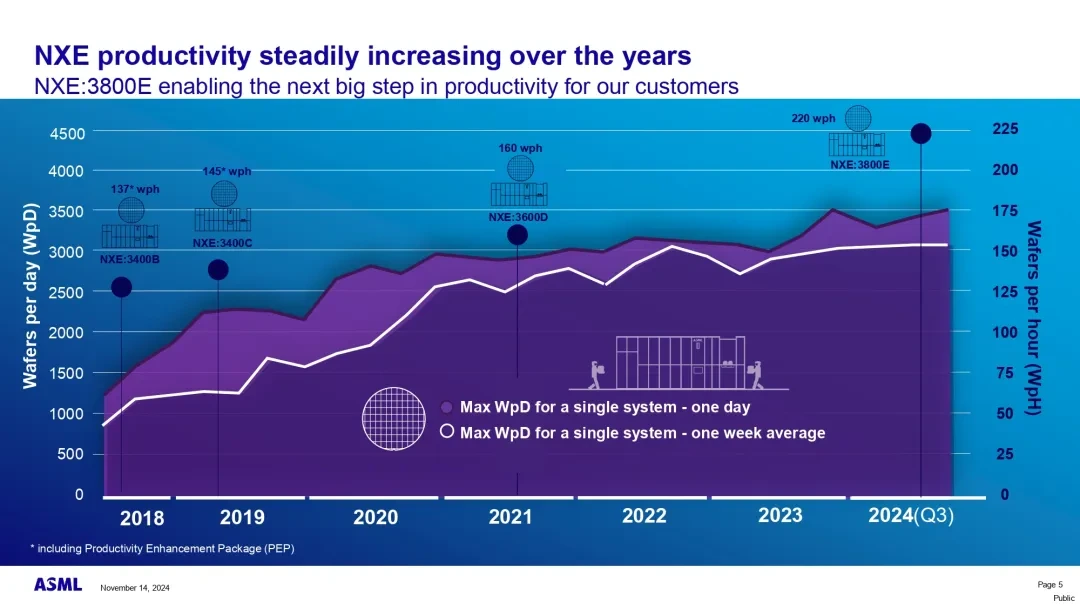

전 세계적으로 0.33 NA EUV 시스템의 평균 가용성은 93.5%를 넘어섰으며 95% 목표를 향해 순조롭게 진행되고 있습니다. 이러한 고가용성은 생산 라인의 안정성과 연속성을 보장하여 반도체 제조업체에 신뢰할 수 있는 보증을 제공합니다. 동시에 NXE:3800E 시스템은 하루 최대 500개의 웨이퍼와 주당 평균 225개의 웨이퍼를 처리하여 생산성이 매우 높습니다.

ASML은 앞으로 EUV 기술 개발을 위한 세부 로드맵을 마련했다. 향후 10년 동안 회사는 0.33NA, 0.55NA 및 잠재적으로 Hyper NA 기술을 경제적으로 확장할 수 있는 고생산성 플랫폼을 출시할 것입니다. 이를 통해 생산 효율성이 크게 향상되고 생산 비용이 절감되며 반도체 제조 산업에 새로운 활력을 불어넣을 것입니다.

EUV 분야의 진주로서 높은 NA EUV 기술에는 고유한 장점이 있습니다. 더 높은 해상도와 대비는 공정을 단순화하고 선량 요구 사항 및 패턴 결함을 크게 줄여 생산성과 수율을 향상시킵니다. 또한 NA가 높은 EUV는 단일 노출 2D 레이아웃 설계를 지원하여 총 금속층 수를 줄이고 생산 비용을 더욱 절감합니다.

혁신에 관한 한 ASML은 멈추지 않습니다. 이 회사는 향후 몇 년 동안 EUV 소스 전력을 1000W 이상으로 늘려 시스템의 생산성과 효율성을 더욱 향상시킬 계획입니다. 동시에 ASML은 광학 및 스테이지 기술을 최적화하여 더 높은 생산성을 달성합니다. 고수율 플랫폼에 고투과 광학 부품을 적용함으로써 투과 효율성과 생산성이 크게 향상되어 반도체 제조 산업에 혁명적인 변화를 가져왔습니다.

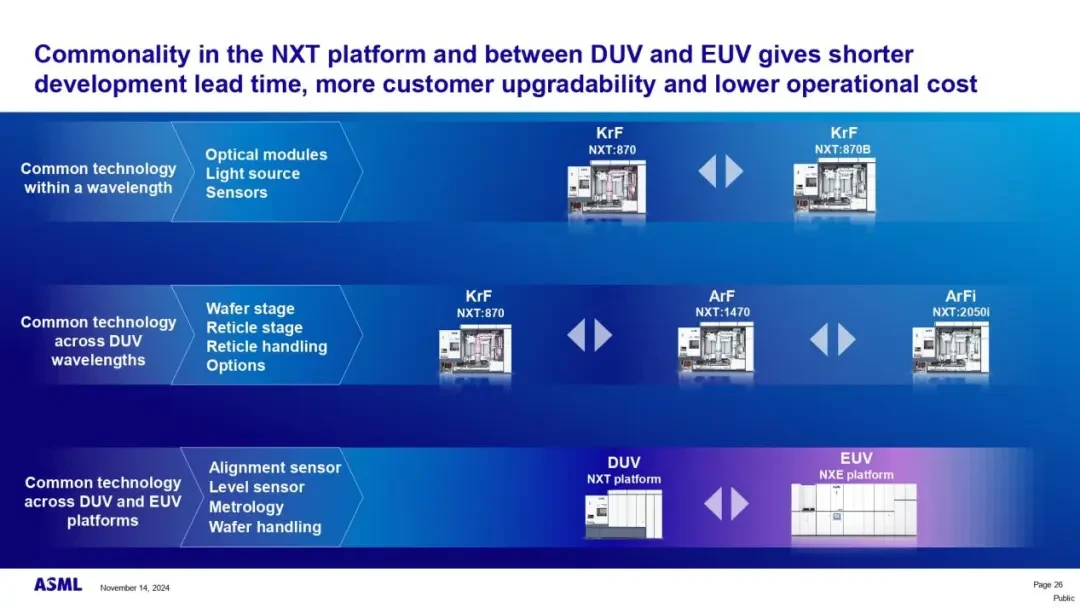

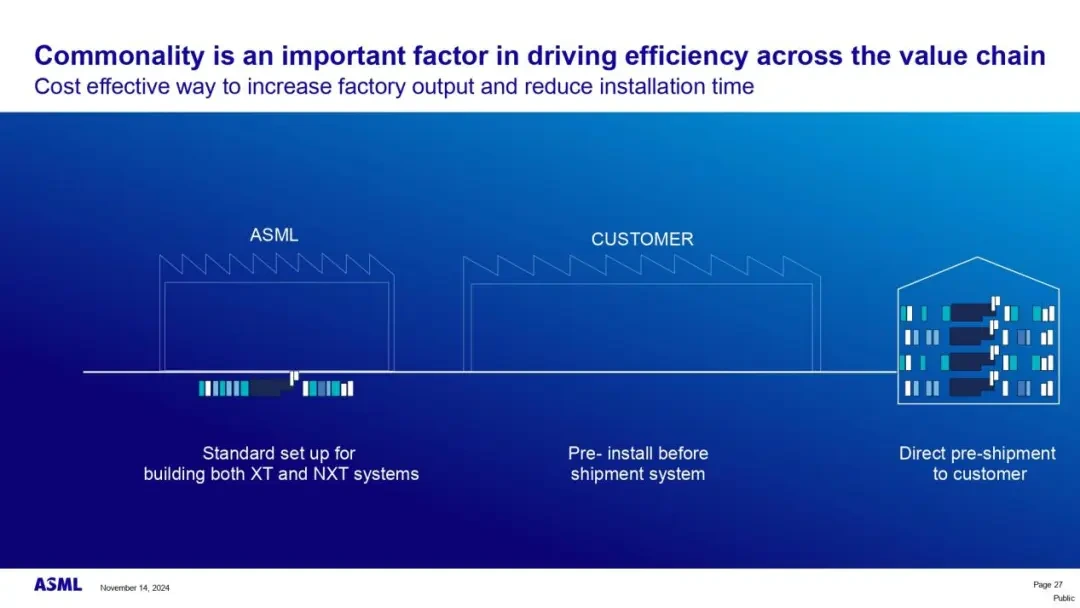

또한 ASML은 모듈식 프레임워크 아키텍처를 통해 제품 믹싱의 유연성을 달성할 계획입니다. 이 아키텍처를 사용하면 서로 다른 제품 라인에서 기술과 리소스를 공유할 수 있으므로 전반적인 효율성이 향상되고 비용이 절감됩니다. 이를 통해 ASML의 시장 경쟁력을 강화할 뿐만 아니라 고객에게 보다 유연하고 효율적인 제품 옵션을 제공할 수 있습니다.

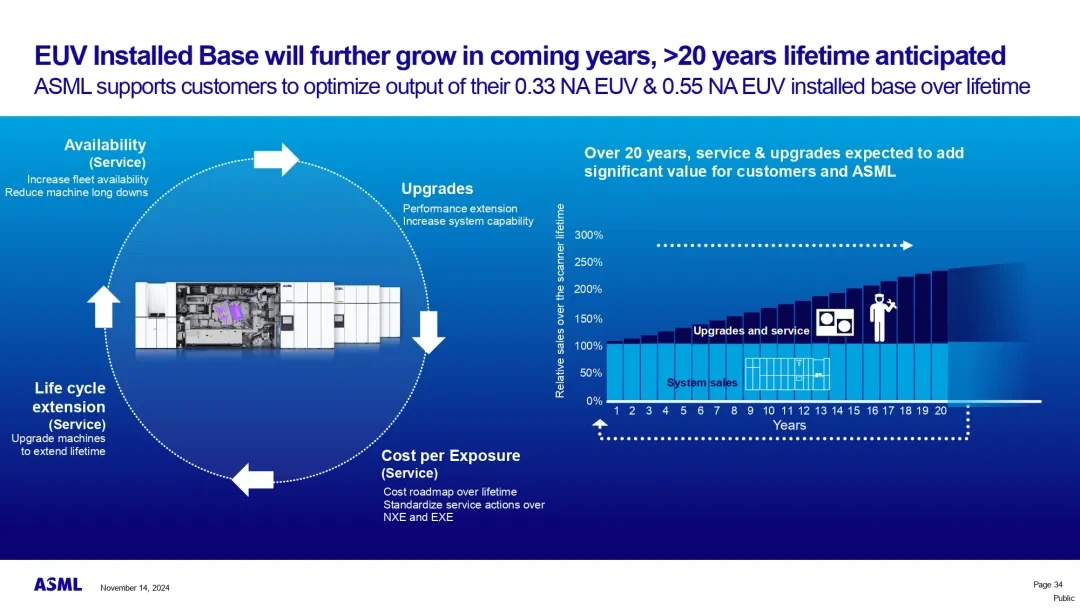

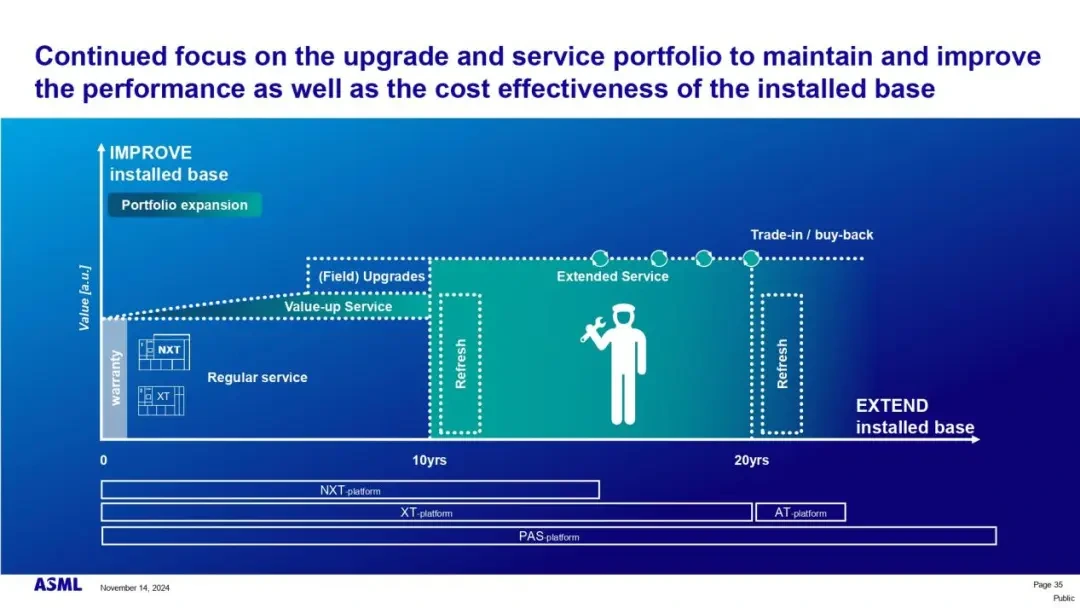

마지막으로, ASML은 수명 주기 전반에 걸쳐 고객의 EUV 설치 기반 최적화를 지원하겠다는 약속도 강조합니다. 이 회사는 장비의 수명을 연장하고 가치를 높이기 위해 업그레이드 및 서비스를 제공하여 고객에게 더 큰 경제적 이익을 창출합니다.

핵심 메시지:

- 극자외선(EUV) 기술은 대량 생산의 성숙 단계에 도달하여 지속적인 혁신을 위한 견고한 기반을 제공합니다.

- NXE:3800E는 이전보다 생산성이 38% 향상되고 정확도가 13% 향상되었으며, NXE:4000F와 그 후속 제품은 향후 생산성과 정확도를 더욱 향상시킬 것입니다.

- imec ASML의 High NA EUV Lab은 6월에 문을 열었으며 모든 EUV 고객은 주요 계층에 노출되었습니다. 데이터에 따르면 이 시스템은 0.33NA에 비해 중요 레이어 비용을 줄이는 데 20-35%의 이점이 있으며, 이는 주로 감소된 노출량, 단일 노출 및 2D 레이아웃 설계 지원으로 인해 발생합니다.

- 최초의 high-NA EUV 시스템이 고객 현장에서 사용되었으며, 이는 high-NA EUV 기술 채택에 있어 중요한 이정표가 되었습니다.

- 미래에는 0.33 NA 및 0.55 NA EUV 시스템이 중요한 노출에 함께 사용될 것입니다. 향후 10년간의 EUV 로드맵에는 0.33 NA, 0.55 NA 및 잠재적으로 Hyper NA 기술의 경제적인 확장을 지원하는 고생산성 플랫폼의 출시가 포함됩니다.

- 생산성과 성능 업그레이드를 결합함으로써 증가하는 설치 기반은 가치 기반 서비스 모델을 통해 완전히 활용될 것입니다.

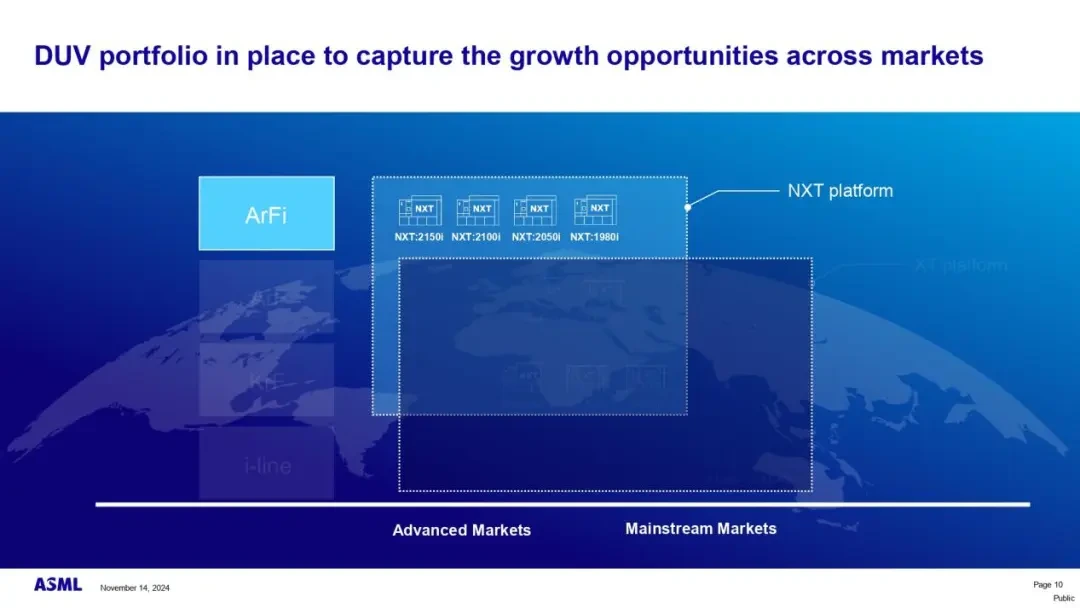

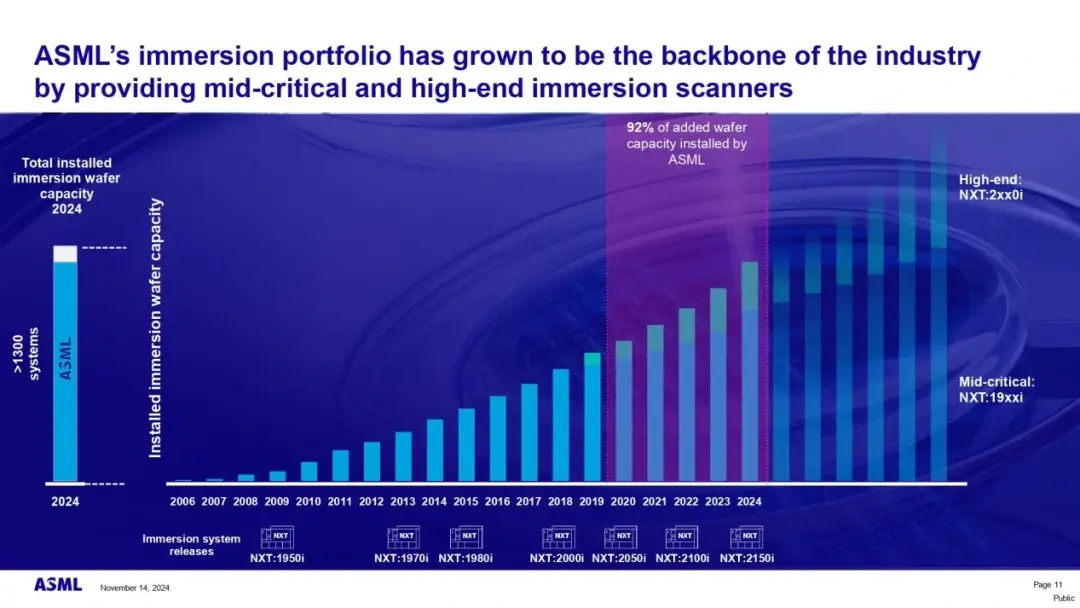

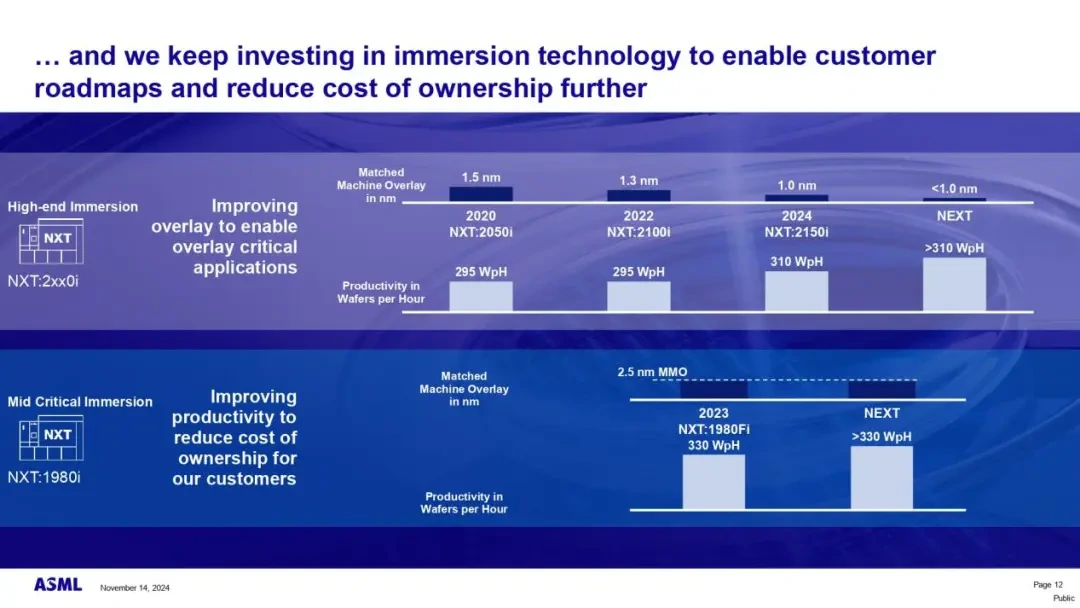

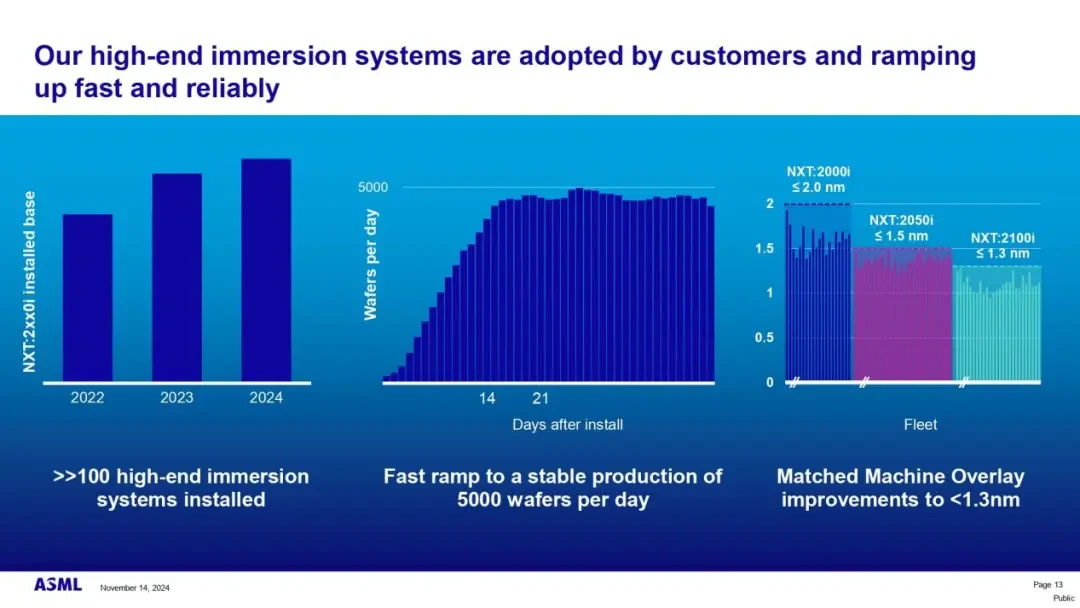

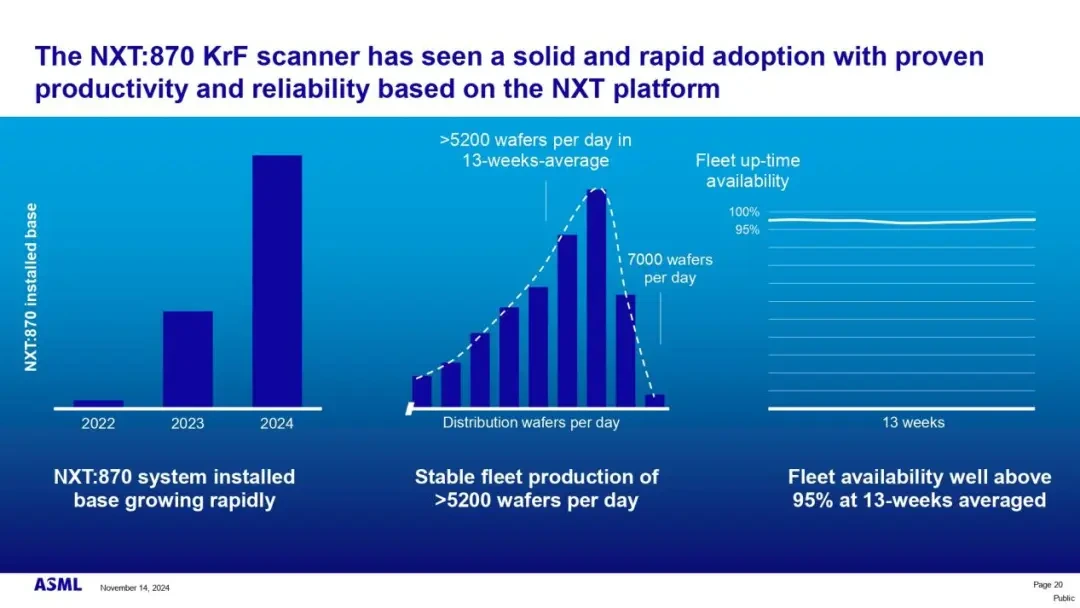

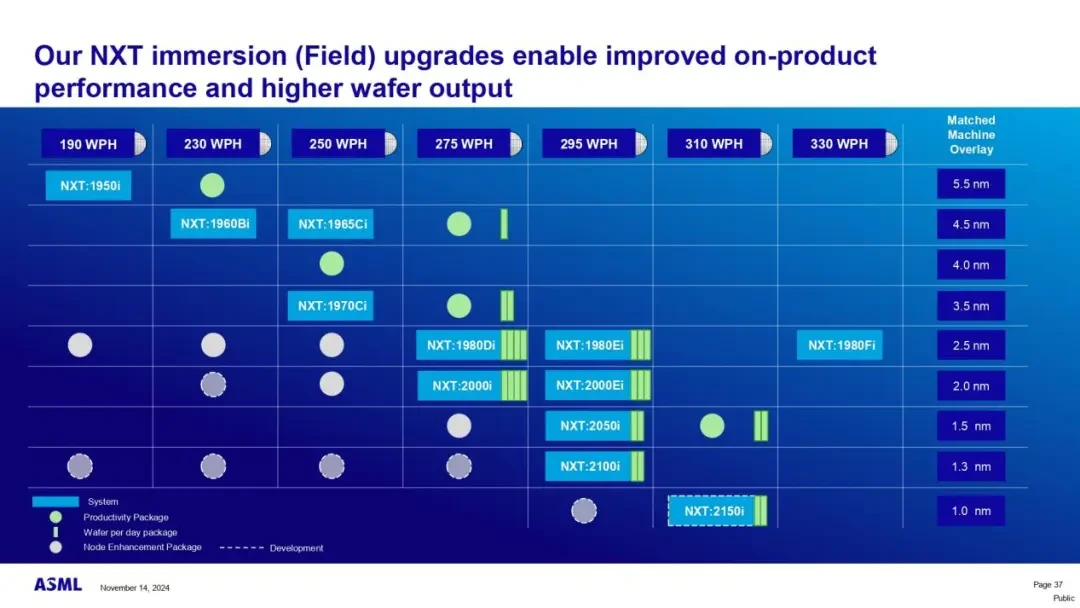

DUV 제품 및 비즈니스 기회

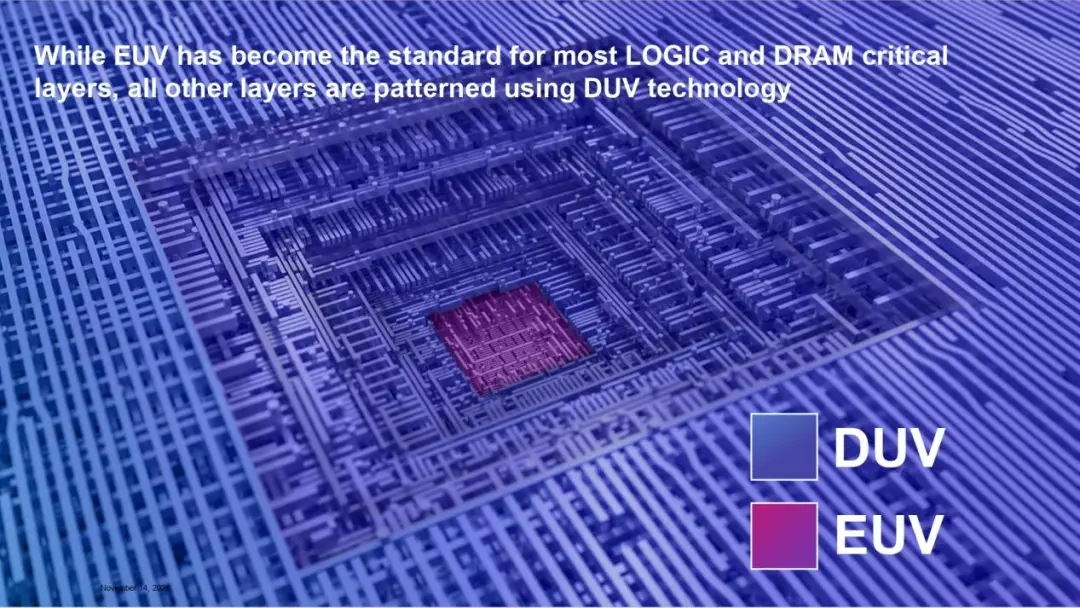

반도체 산업 기술의 급속한 발전의 물결 속에서 DUV(Deep Ultraviolet) 리소그래피 기술은 대체할 수 없는 위치로 전체 산업의 발전을 확고하게 지원하고 있습니다. EUV(Extreme Ultraviolet) 기술이 로직 및 DRAM 크리티컬 레이어의 최전선에 서고 있는 가운데, DUV 기술은 광범위한 적용 가능성, 유연성 및 효율성으로 인해 여전히 업계의 견고한 초석으로 남아 있습니다.

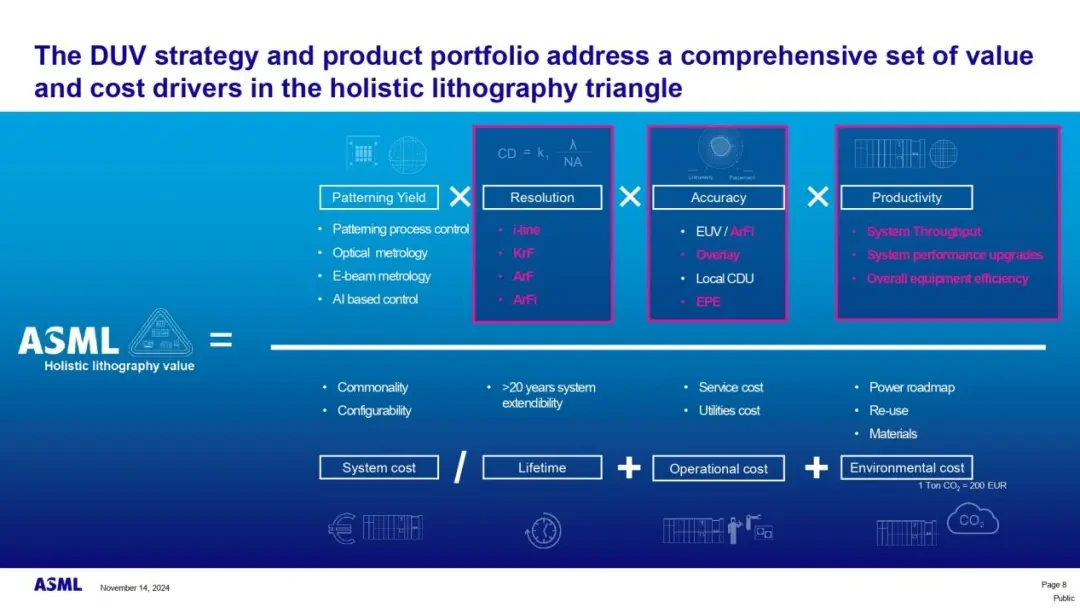

DUV 기술의 중요성과 시장 지위는 자명합니다. 현재의 리소그래피 환경에서는 중요하지 않은 레이어 및 대부분의 다른 레이어를 패터닝하기 위한 첫 번째 선택일 뿐만 아니라 고급형에서 주류 시장에 이르기까지 광범위한 응용 분야에서 필수적인 역할을 합니다. ASML의 연구 데이터는 이를 더욱 확증하며, 웨이퍼 수요가 증가하고 층당 리소그래피 지출이 증가함에 따라 DUV 기술은 미래 시장 성장에 계속해서 크게 기여할 것입니다.

DUV 기술과 제품 혁신의 장점은 지속적인 리더십의 핵심입니다. XT 및 NXT 건식 DUV 제품군과 같은 다양한 제품 포트폴리오는 고객에게 유연한 성능 옵션을 제공하고 다기능성과 운영 효율성을 높여 기술 비용을 최적화합니다. 동시에 DUV 기술은 다양한 시장 요구를 충족하기 위해 제품 포트폴리오를 지속적으로 확장하고 있으며, 새로운 i-line 광시야 스캐너는 생산성 및 고급 패키징 응용 분야에서 새로운 산업 표준을 설정합니다.

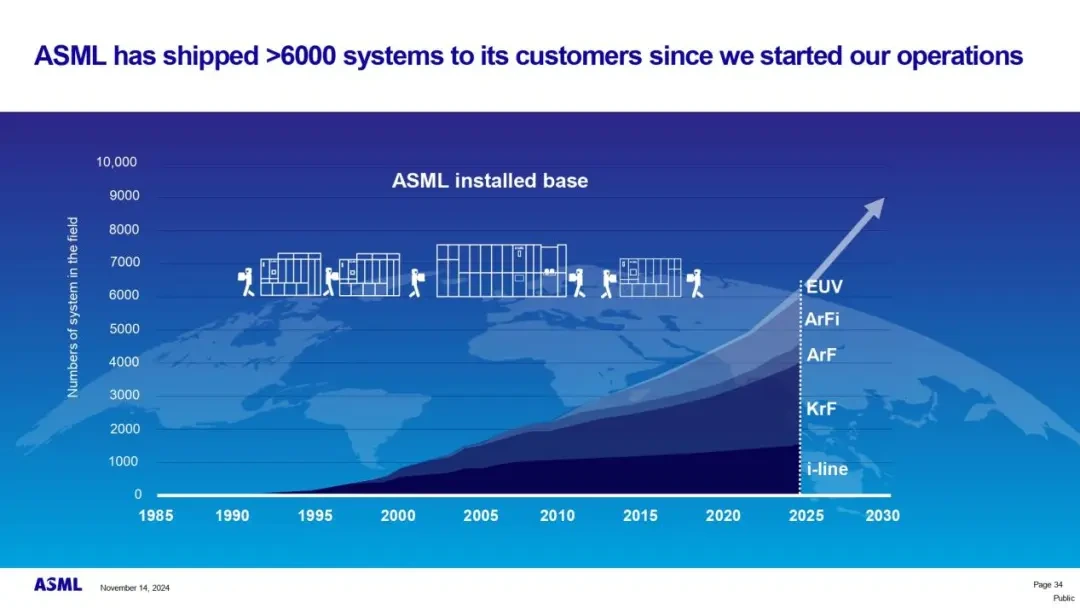

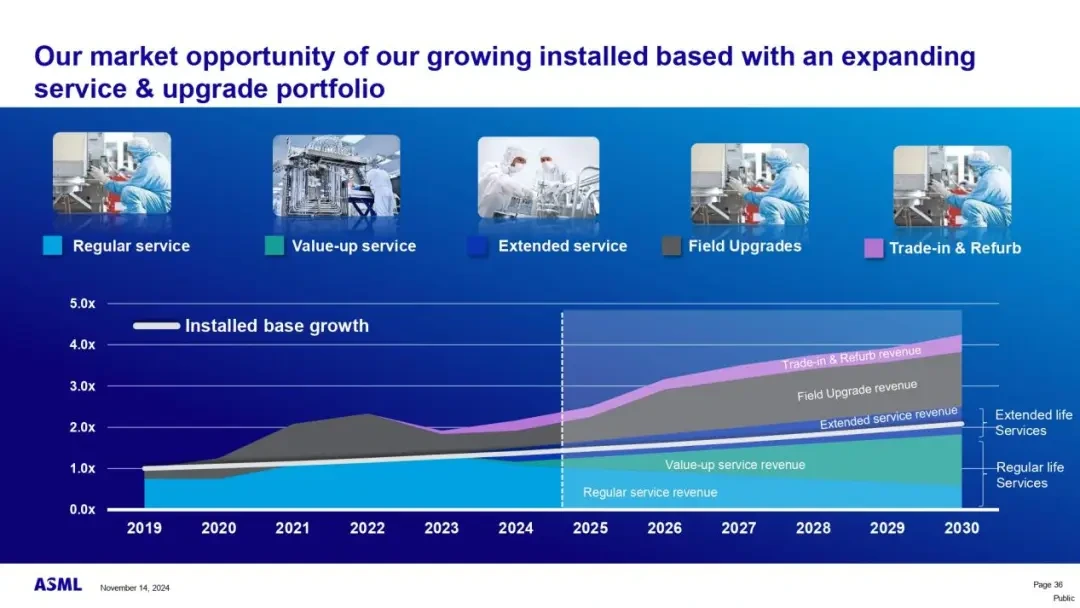

생산성 최적화와 관련하여 ASML은 전 세계 6,000개 이상의 DUV 시스템의 설치 기반 수명을 20년 이상으로 연장하고 고객이 서비스 및 업그레이드를 통해 총 소유 비용을 절감할 수 있도록 지원하기 위해 최선을 다하고 있습니다. 이러한 연속성은 고객의 투자 수익률을 향상시킬 뿐만 아니라 DUV 기술의 지속 가능성 잠재력을 강조합니다.

DUV 기술은 비용과 성능 간의 최상의 균형을 제공하므로 복잡한 반도체 장치를 제조하는 데 중요한 도구입니다. EUV 기술과의 비교는 가격 대비 성능, 장비 성숙도 및 운영 유연성 측면에서 DUV의 상당한 이점을 보여주며, 이는 중요하지 않고 다양한 응용 분야에서 매우 경쟁력이 있습니다.

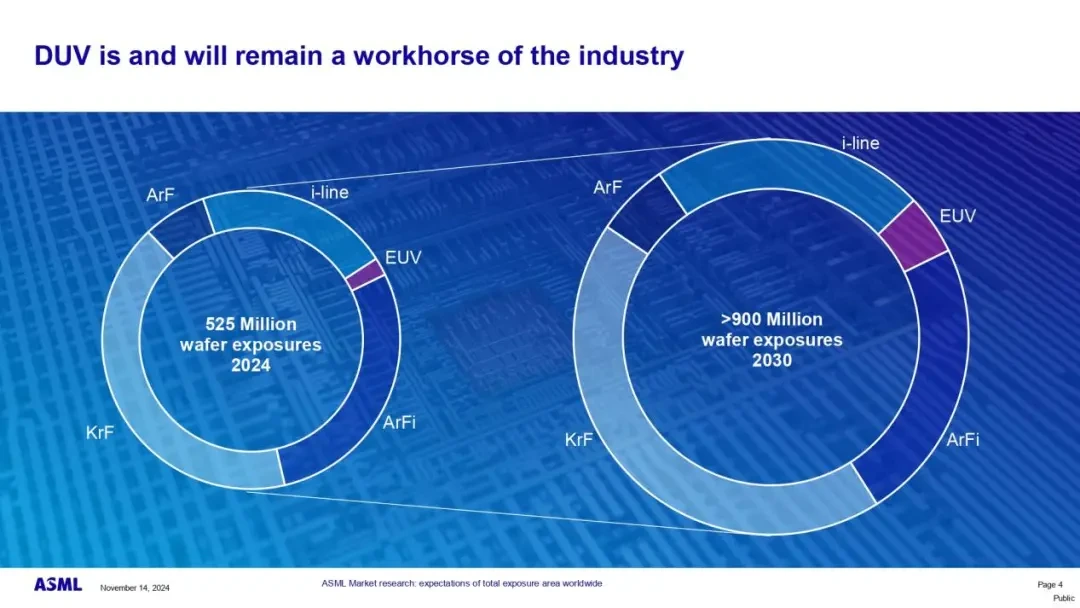

앞으로 DUV 기술의 지속적인 발전은 더 많은 기회를 얻을 것입니다. ASML은 2030년까지 전 세계적으로 DUV 기술이 지원하는 웨이퍼 임프레션 수가 9억 개를 초과할 것으로 예상하고 있으며, 이는 DUV 기술에 대한 시장 수요를 강조할 뿐만 아니라 미래 기술 진화를 위한 명확한 방향을 제시하는 목표입니다. 시장에서의 리더십 입지를 공고히 하기 위해 ASML은 고객의 소유 비용을 더욱 절감하고 기술 로드맵을 지원함으로써 DUV 침지 기술에 대한 투자를 지속적으로 늘릴 것입니다.

반도체 산업의 중요한 기둥인 DUV 기술은 광범위한 시장 적용 가능성과 지속적인 혁신적인 제품 이점으로 향후 몇 년 동안 업계를 계속 주도할 것입니다. 하이엔드 칩 제조든 주류 시장 수요든 DUV 기술의 유연성과 효율성은 더 많은 기회를 얻을 것입니다. 기술의 지속적인 발전과 시장 수요의 지속적인 성장으로 DUV 기술은 미래의 리소그래피 기술 환경에서 계속해서 필수적인 역할을 할 것입니다.

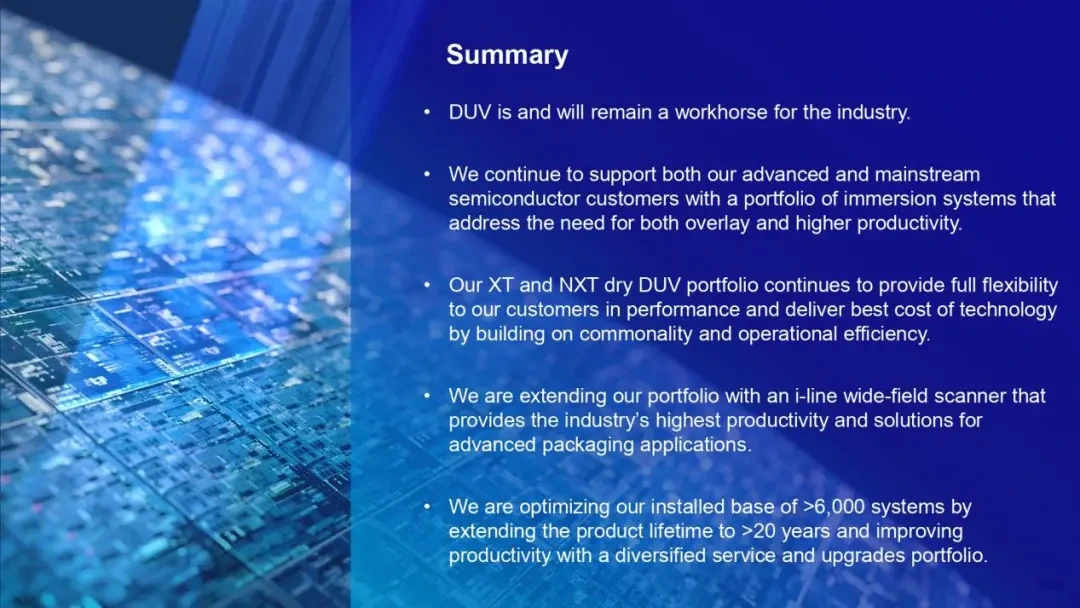

요약:

- 심자외선(DUV) 기술은 계속해서 업계의 주요 동력이 될 것이며 미래에도 계속해서 중요한 역할을 할 것입니다.

- 우리는 적층 정확도와 더 높은 생산성에 대한 요구 사항을 충족하는 몰입형 시스템 포트폴리오를 제공함으로써 고급 및 주류 반도체 고객을 계속 지원하고 있습니다.

- 로크웰 오토메이션의 XT 및 NXT 드라이 DUV 포트폴리오는 다목적성과 운영 효율성을 구축함으로써 성능 측면에서 최고의 기술 비용을 제공할 수 있는 완전한 유연성을 고객에게 지속적으로 제공하고 있습니다.

- 당사는 업계 최고의 생산성을 제공하고 고급 패키징 응용 분야를 위한 솔루션을 제공하는 i-line 광시야 스캐너로 포트폴리오를 확장하고 있습니다.

- 우리는 제품 수명 주기를 20년 이상으로 연장하고 다양한 서비스 및 업그레이드 포트폴리오를 통해 생산성을 높임으로써 6,000개 이상의 시스템 설치 기반을 최적화합니다.

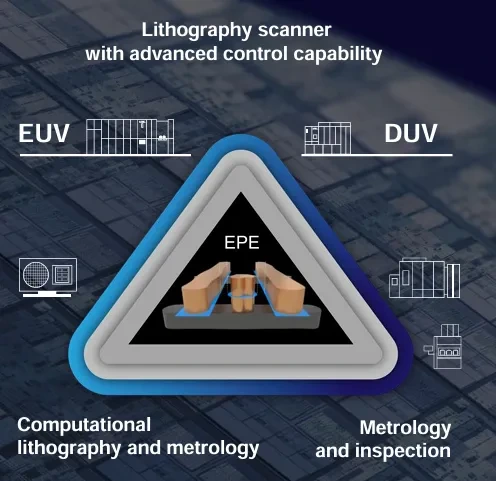

전체론적 리소그래피 솔루션 및 비즈니스 기회

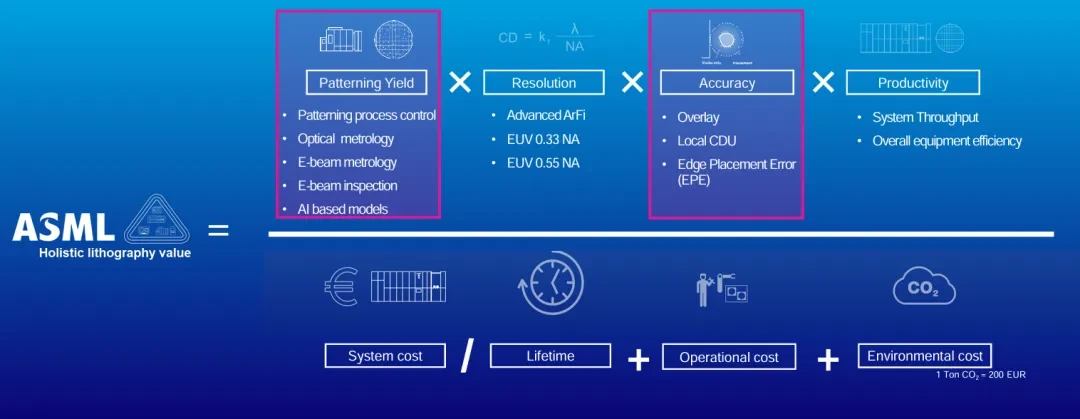

"Total Lithography Solutions and Business Opportunities"라는 토론에서 ASML의 부사장 겸 비즈니스 라인 애플리케이션 책임자인 Marco Pieters는 전반적인 리소그래피 기회와 성장 동인을 강조했습니다.

- 일체형 리소그래피는 고객을 위해 정확도와 패턴 수율을 개선하는 데 중점을 둡니다.

- 계측 및 검사 및 스캐너 정확도: 컴퓨터 리소그래피(물리적 모델 및 AI) 최적화를 통해 적층 및 가장자리 배치 오류(EPE)를 개선합니다.

- 스케일업: 2D 및 3D 구조를 위한 비용 효율적인 계측 및 검사 솔루션으로 조기 수율 램프 및 전체 리소그래피 제어를 가능하게 합니다.

- 다중 빔 감지에서 상당한 진전이 이루어졌으며 HVM에 대한 기회를 제공하며, 첫 번째 응용 분야는 전압 대비 감지가 될 것입니다.

- 그 다음에는 매립 결함 감지가 필요한 더 작은 2D 피처와 3D 구조가 뒤따릅니다.

- 계측 및 제어 솔루션과의 프런트 엔드 3D 통합(웨이퍼 본딩)을 통해 고객의 패턴 정렬 정확도 요구 사항을 충족합니다.

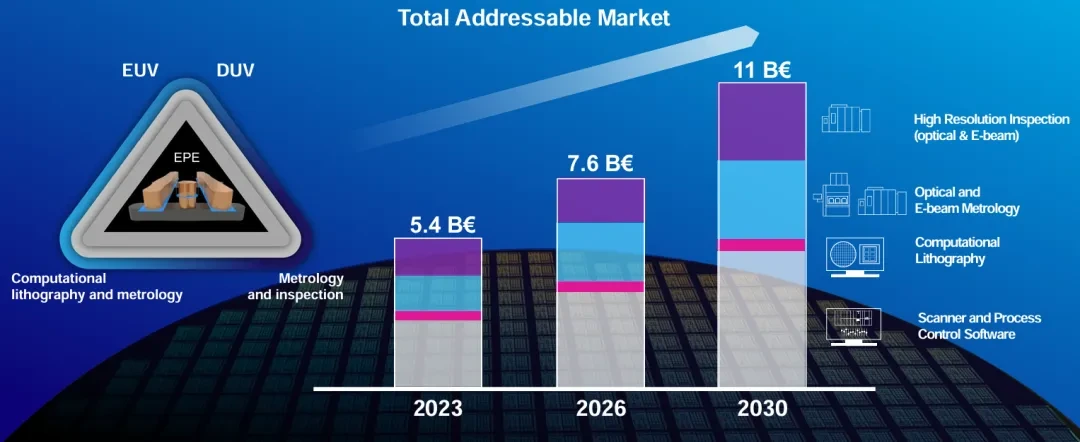

- 전체 리소그래피 사업은 2025년에서 2030년 사이에 15% 이상의 연평균 성장률로 성장할 것으로 예상되며 총 마진은 여전히 강세를 유지할 것으로 예상됩니다.

ASML의 제품 포트폴리오는 패턴화된 수율과 정확성에 중점을 두고 있으며, 일체형 리소그래피를 통해 ASML의 고객은 고품질 라운드를 극대화하여 시스템 비용, 수명 주기, 운영 및 환경 비용과 같은 여러 측면에서 도움을 받을 수 있습니다.

무어의 법칙이 발전함에 따라 논리적 로드맵은 계속해서 수축을 촉진하고, 가장자리 배치 오류를 개선하고, 금속 간격을 줄이고, 접착 후 오버레이를 조여야 하므로 요구 사항이 증가하고 있습니다.

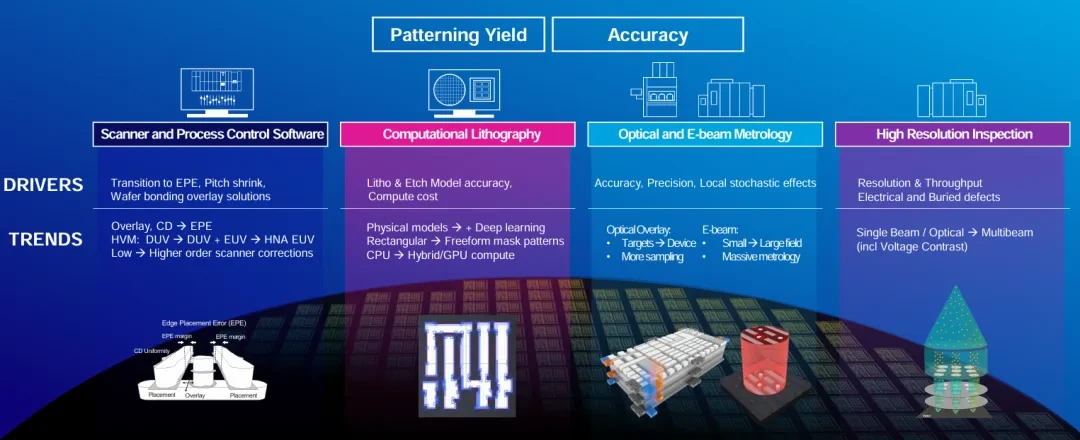

진화하는 산업 로드맵은 ASML의 제품 성장을 위한 새로운 기회를 제공합니다. 예를 들어:

- 스캐너 및 공정 제어 소프트웨어: EPE, 피치 수축, 웨이퍼 본딩 커버리지 솔루션 등에 의해 발생하는 임계 치수(CD) 오류에서 가장자리 배치 오류(EPE)로 이동; DUV에서 DUV+EUV 및 High-NA EUV로의 추세는 진화하고 있습니다. 저차에서 고급 스캐너 보정이 개발되었습니다.

- 컴퓨테이셔널 리소그래피(Computational lithography): 리소그래피 및 에칭 모델의 정확성과 계산 비용에 힘입어 물리적 모델은 딥 러닝으로, 직사각형 마스크는 무료 그래픽으로, CPU는 하이브리드 본딩 GPU 컴퓨팅으로 진화하고 있습니다.

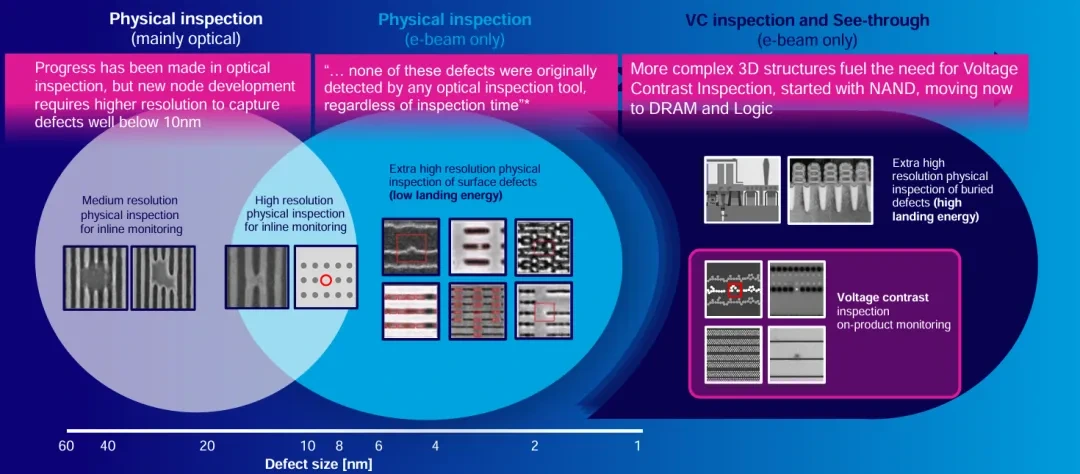

- 광학 및 전자빔 계측: 정확성, 정밀도, 국소 랜덤 효과 등에 대한 요구로 인해 광학 커버리지 및 전자빔에 대한 새로운 요구 사항이 도입되고 있습니다.

- 고해상도 검사: 분해능, 전자 처리량 및 매몰 결함에 힘입어 단일 빔/광학 시스템은 다중 빔으로 이동하고 있습니다.

이러한 추세에 힘입어 총 목표 시장 규모는 2023년 54억 유로에서 2030년 110억 유로로 성장할 것이며 엄청난 시장 잠재력을 가지고 있습니다. 각 기술 부문의 성장 공간은 다음 그림에 나와 있습니다.

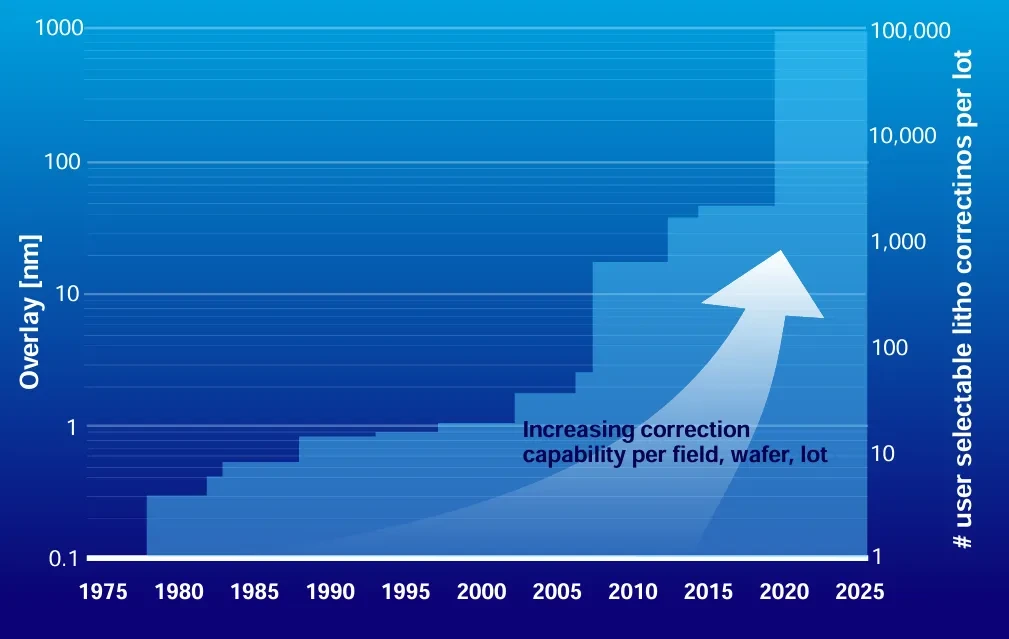

스캐닝 및 공정 제어 소프트웨어 섹션에서 리소그래피는 공정 구조를 보정하기 위한 강력한 도구로, 각 필드, 웨이퍼 및 배치를 보정할 수 있는 기능을 추가하여 보정 기능을 약 5배 증가시키고 오버레이 정렬 기능을 약 3배 증가시킬 수 있습니다.

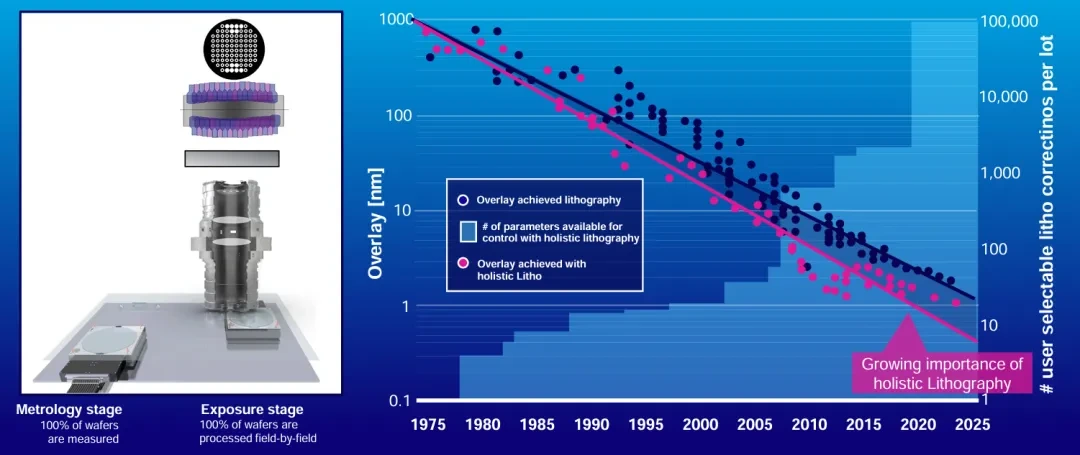

위의 꺾은선형 차트는 시간 경과에 따른 커버리지 정확도의 향상을 보여줍니다. 검은색 점들은 기존의 리소그래피를 사용하여 달성된 커버리지 정확도를 나타내고, 분홍색 점들은 모노리소그래피를 사용하여 달성된 커버리지 정확도를 나타낸다. 최근 몇 년 동안 전반적인 리소그래피 방법이 더 큰 개선 가능성을 보이고 있음을 알 수 있습니다.

전반적으로 시장 수요가 증가하고 스캐닝 및 공정 제어 소프트웨어의 발전으로 일체형 리소그래피의 중요성이 점점 더 두드러지고 있으며 일체형 리소그래피는 커버리지 정확도를 개선하고 가장자리 위치 오류를 줄여 사용자의 생산성과 품질을 향상시키는 데 중요한 역할을 하며, 이는 칩 제조의 수율을 높이는 데 필수적입니다.

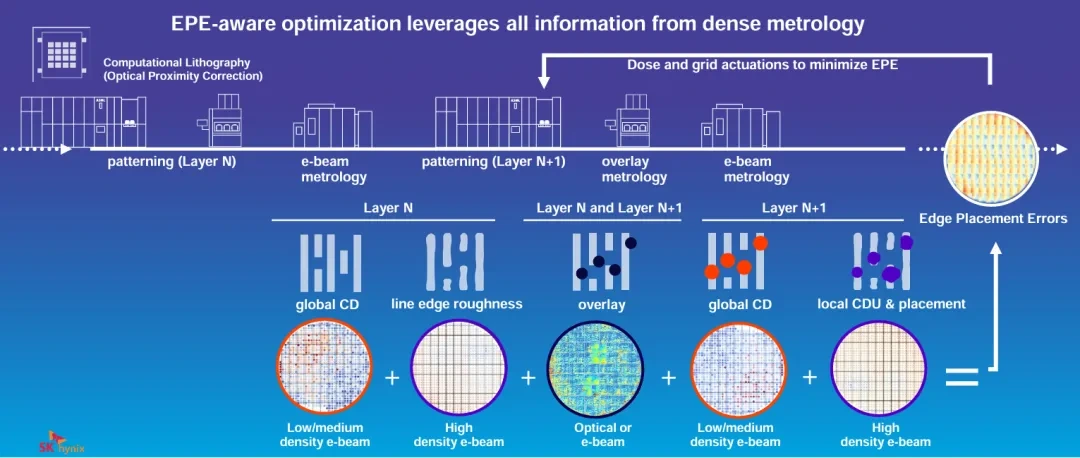

컴퓨터 리소그래피에서 광학 근접 보정의 정확도는 기계 학습과 질량 계측의 도입 덕분에 빠르게 향상되었습니다. 전체 프로세스는 밀집된 계측 데이터와 스캐너 움직임을 활용하여 엣지 배치 오류를 최소화함으로써 패턴 수율을 최적화합니다.

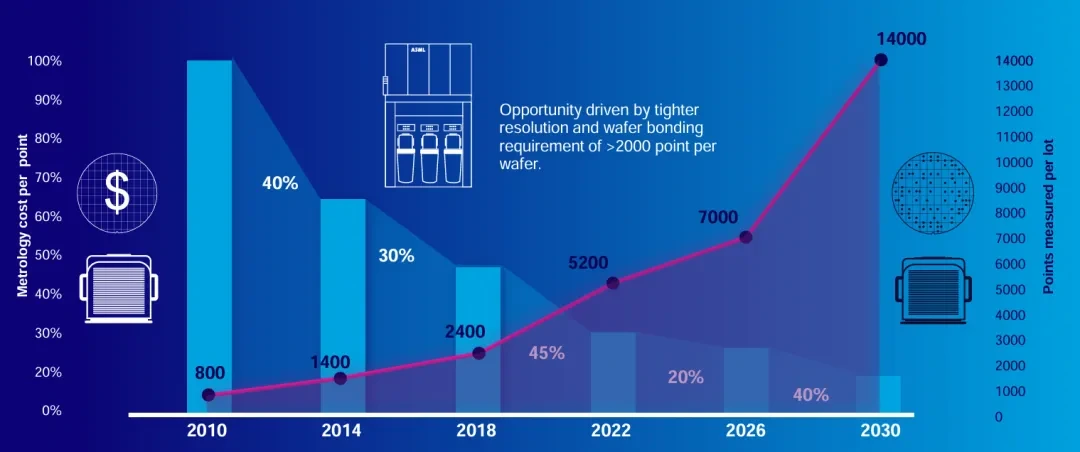

동시에 이러한 스캐너 보정을 수행하기 위해 많은 수의 오버레이 계측이 필요합니다. ASML의 YieldStar 플랫폼은 4년마다 샘플링 볼륨을 80%씩 늘리고 비용 효율성을 30~45% 향상시킬 수 있습니다.

ASML의 YieldStar 시스템은 고객이 수율을 개선, 즉 웨이퍼에서 적격 칩의 비율을 늘리는 데 도움이 될 수 있는 것으로 이해됩니다. YieldStar를 통해 제조업체는 오버레이 정확도(칩 레이어 간 적층 정확도)와 같은 중요한 생산 매개변수를 추적할 수 있으며, 이러한 매개변수는 종종 빠르고 정확한 검사를 위해 생산 라인에 통합되며, 제조 공정의 실시간 수정을 위해 적시 데이터가 리소그래피 시스템에 피드백됩니다.

이 방법은 패턴 형성 프로세스를 효과적으로 최적화하고 다양한 계측 도구와 데이터를 결합하여 패턴의 품질과 일관성을 향상시킬 수 있습니다. ASML은 2024년 상반기에 1,000세트 이상의 YieldStar 시스템을 설치한 것으로 밝혀졌습니다.

패턴화된 수율: 전자빔이 물리적 및 매몰 결함과 전압 대비를 감지할 수 있는 기회로, 대량 제조에서 전자빔 검사의 사용을 주도하고 있습니다.

위의 다이어그램은 계측 데이터와 스캐너 움직임을 결합하여 그래프 수율을 최적화하는 과정을 보여줍니다. 구체적인 단계는 다음과 같습니다.

- Computational Lithography: Optical Proximity Correction을 사용한 패터닝(레이어 N).

- e-beam metering: e-beam metering을 수행하여 레이어 N 데이터를 얻습니다.

- 패터닝(레이어 N+1): 얻은 데이터를 사용하여 다음 레이어를 패터닝합니다.

- 오버레이 계측: 레이어 N 및 레이어 N+1에 대한 오버레이 계측.

- 전자빔 측광(레이어 N+1): 전자빔 측광을 다시 수행하여 레이어 N+1 데이터를 얻습니다.

위의 단계를 통해 Edge Placement Errors의 최적화가 이루어졌습니다. 계측 데이터와 스캐너 동작의 조합을 사용하여 패턴 수율을 최적화하는 방법, 특히 조밀한 패턴의 경우 수율을 개선하고 가장자리 배치 오류를 줄이는 방법을 보여줍니다.

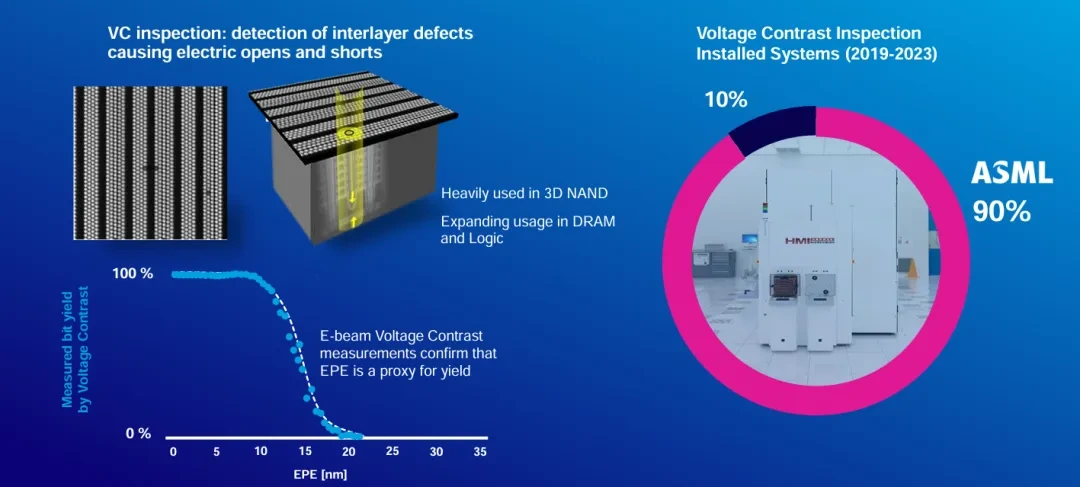

NAND HVM은 차동 전압 센싱 기술을 사용하며 로직 및 DRAM 영역으로 점차 확장되고 있습니다. 전자빔 검사 기술은 수율 저하로 이어지는 결함을 찾아낼 수 있는 고유한 능력을 가지고 있습니다.

위의 다이어그램은 전압 대비 감지 기술을 사용하여 수율을 높일 수 있는 기능을 보여줍니다. 그림은 두 부분으로 나뉩니다.

왼쪽 부분:

- NAND 및 DRAM에서 전압 대비 감지 기술의 광범위한 적용을 보여줍니다.

- 이는 이 기술이 층간 단락을 일으키는 결함을 찾는 데 매우 효과적임을 시사합니다.

- 전압 대비 감지 기술의 고유한 기능이 강조됩니다.

오른쪽 부분:

- ASML에서 설치한 전압 대비 감지 시스템의 사진이 표시됩니다.

- 이 기술의 응용 범위는 특히 로직 및 DRAM에서 확장되고 있습니다.

일반적으로 전압 대비 감지 기술은 NAND와 DRAM에 널리 사용되어 왔습니다. 이 기술은 전기 단락을 일으키는 결함을 감지하는 데 특히 적합합니다. ASML의 전압 대비 감지 시스템은 설치 및 운영되고 있으며, 그 고유한 기능은 생산량을 늘리는 효과적인 수단이 되고 있습니다.

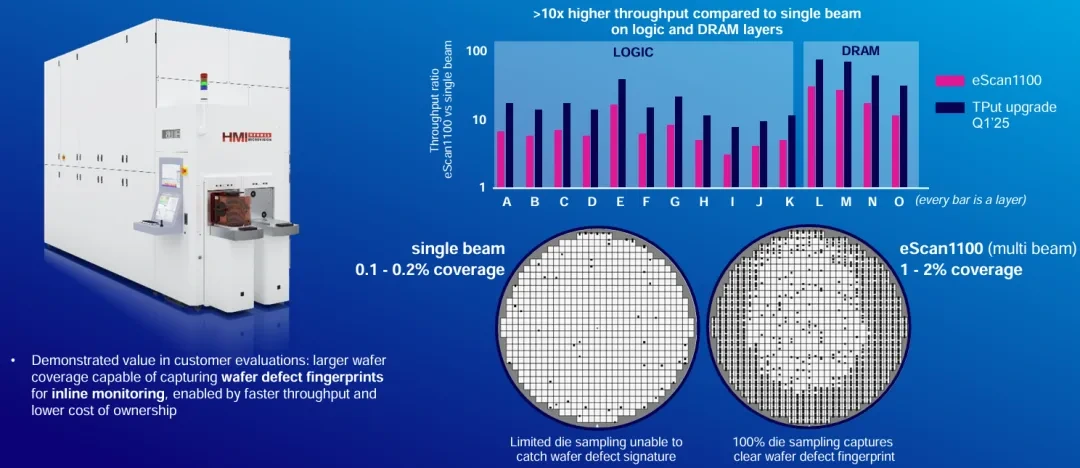

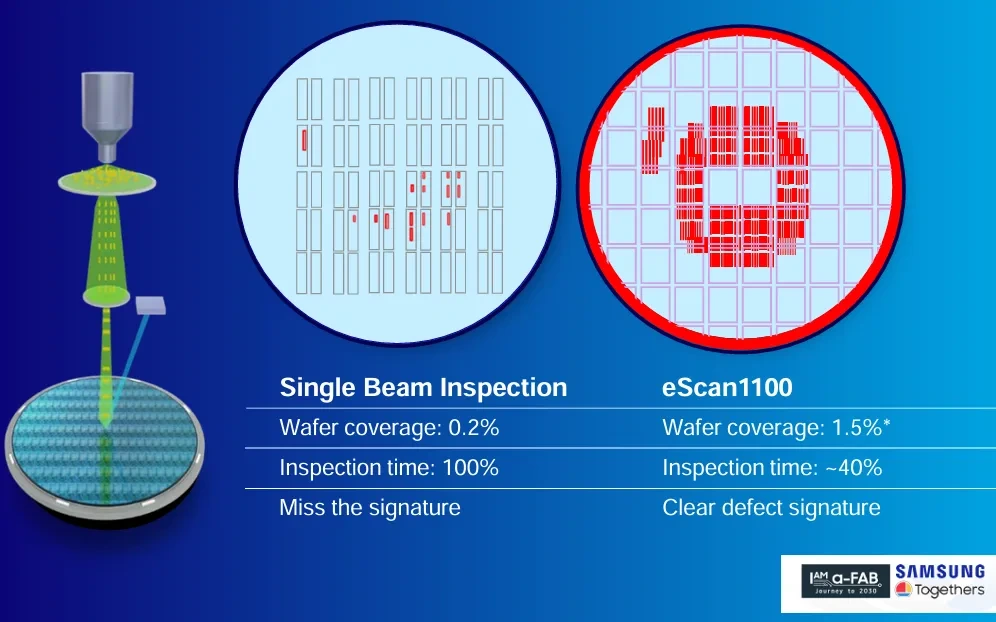

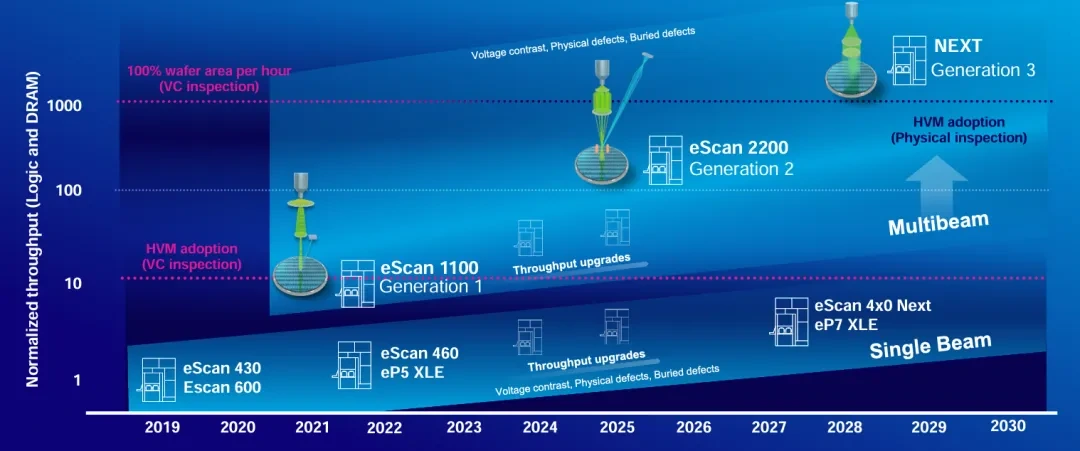

멀티빔 eScan 1100은 웨이퍼 커버리지가 더 크고 CoO 성능이 우수하며 처리량이 10배 이상 증가하는 것으로 이해됩니다. HVM(High-Volume Metal)의 전압 비교 평가 및 검증을 위한 10대의 eScan11100 시스템이 5개 고객사에서 사용되었습니다.

고객 데이터에 따르면 eScan1100은 더 높은 처리량에서 명확한 결함 특징을 캡처합니다. 웨이퍼 커버리지는 7~8배 증가하고, 사이클 타임은 약 60% 단축됩니다.

멀티빔은 HVM의 인라인 결함 모니터링을 위한 전압 대비 및 물리적 검사 측면에서 더 높은 처리량과 더 큰 웨이퍼 적용 범위를 가능하게 합니다.

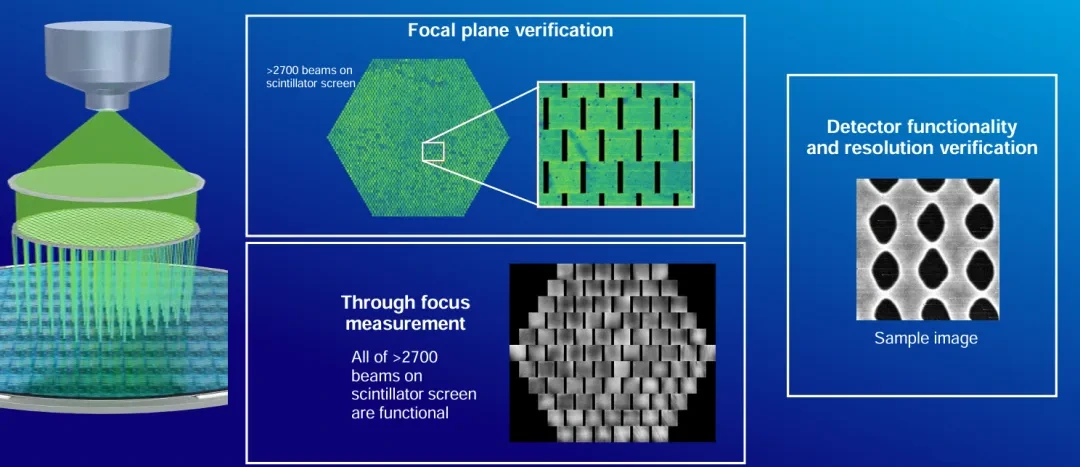

미래의 혁신을 위해 멀티빔 진화의 다음 단계는 25개의 빔에서 2,700개 이상의 빔으로 확대되는 것이며, 2025년에 고객에게 출시하는 것을 목표로 하고 있습니다.

ASML은 프론트엔드 3D 통합이 2D 드라이브 밀도의 축소를 보완할 것으로 기대하고 있으며, 프론트엔드 3D 통합 챌린지는 모든 반도체 제품에 새로운 리소그래피 기회를 제공할 것입니다.

일체형 리소그래피는 3D 통합을 가능하게 하여 접합 전후에 중요한 공정 지점의 필요한 계측 및 스캐너 제어를 다룹니다. 아래 다이어그램은 웨이퍼 본딩 전후에 스캐너 및 오프라인 계측을 통해 웨이퍼 간 패턴 매칭 및 오류 제어, 스캐너 수정 및 제어를 보장하는 프로세스를 보여줍니다.

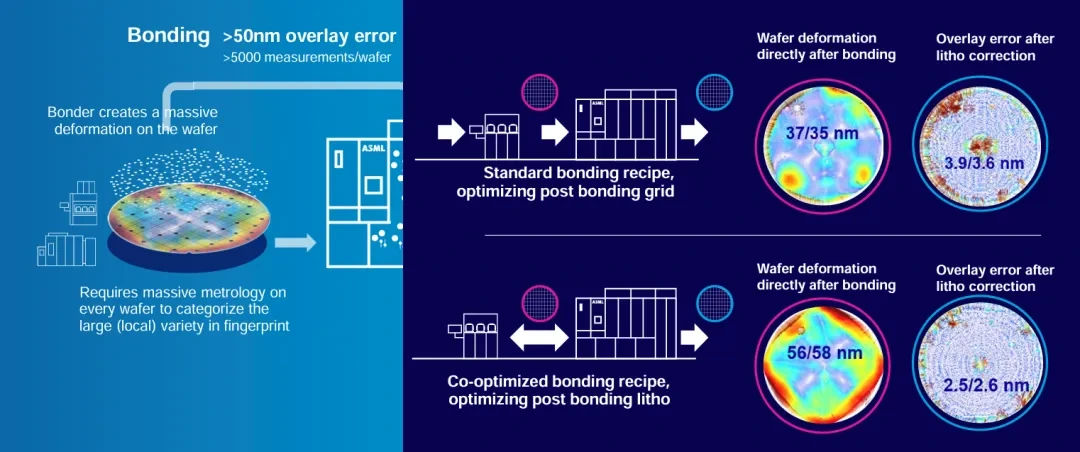

Marco Pieters는 표준 본딩 방식과 최적화된 본딩 메시를 사용하여 웨이퍼 본딩 중 커버리지 오류를 줄이는 프로세스를 설명합니다. 여기에는 다음이 포함됩니다.

접착 전 준비:

- 본더는 웨이퍼에 거대한 변형을 일으킵니다.

- 지문의 다양성을 식별하기 위해 각 웨이퍼에 대한 대규모 계측 지문이 필요합니다.

Standard Bonding Formulations 및 Optimized Meshes After Bonding:

- 커버리지 오류는 표준 접착 공식과 최적화된 접착 메쉬에 의해 감소됩니다.

접합 직후 웨이퍼 변형 측정:

- 웨이퍼 변형은 적시에 조정하고 제어하기 위해 접합 직후에 측정됩니다.

리소그래피 수정 커버리지 오류:

- 접합 효과는 리소그래피 보정 커버리지 오류에 의해 더욱 최적화됩니다.

비즈니스 모델 및 자본 배분 전략

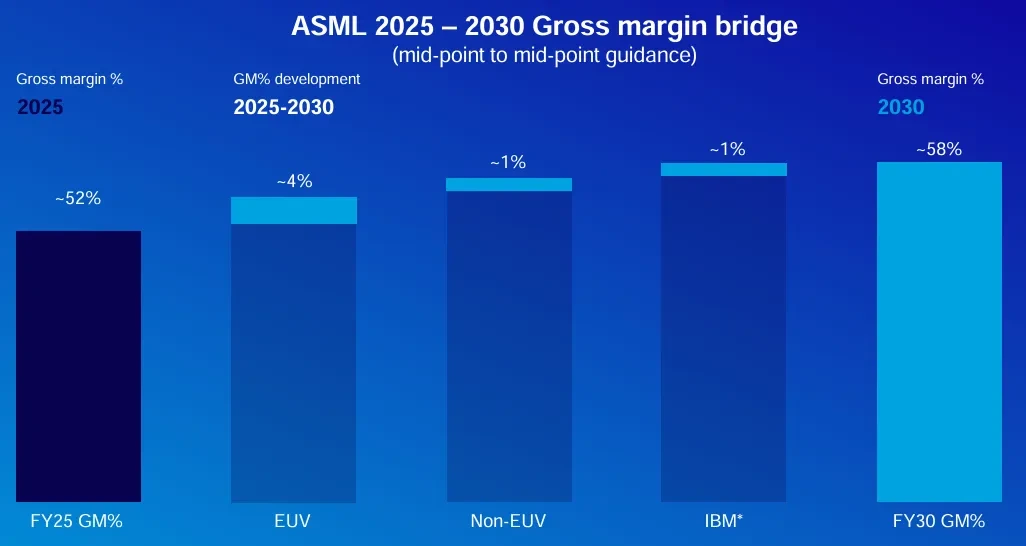

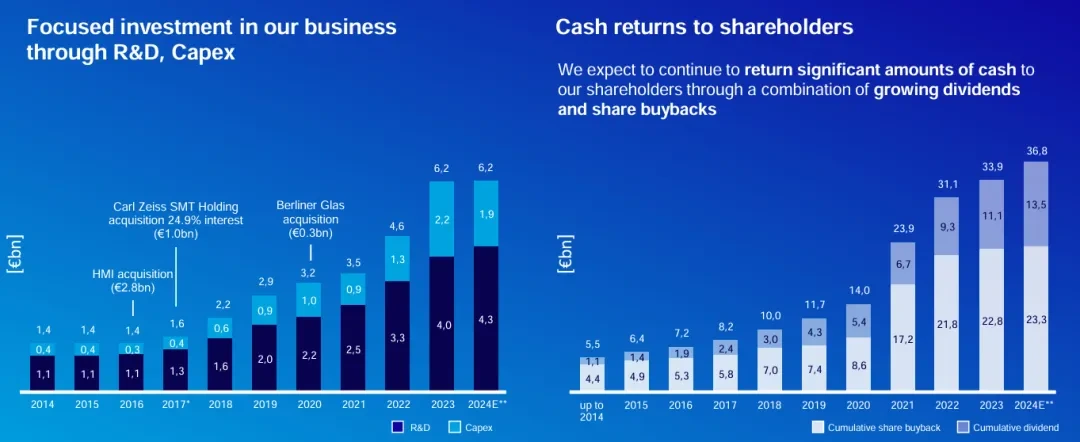

ASML의 최고재무책임자(CFO)인 로저 다센(Roger Dassen)은 비즈니스 모델과 자본 배분 전략에 대한 핵심 메시지를 발표했습니다. 그는 기술 리더십에 대한 ASML의 지속적인 투자가 주주들에게 상당한 가치를 창출했다고 언급했습니다. 반도체 최종 시장의 예상 성장과 미래 노드 리소그래피에 대한 지출 증가는 ASML 제품 및 서비스에 대한 수요를 주도하고 있습니다. ASML은 다양한 시장 및 기술 동향을 바탕으로 2030년까지 연간 약 440억 유로에서 600억 유로의 매출과 약 56%에서 60%의 총 마진을 달성할 것으로 예상합니다.

또한, 자본 배분 및 자금 조달 측면에서 ASML의 자금 조달 정책은 견고한 자본 및 유동성 구조이며, 이를 기반으로 ASML의 사업에 계속 투자할 것이며 배당금 증가 및 자사주 매입을 통해 주주에게 상당한 자금을 환원할 것으로 기대합니다.

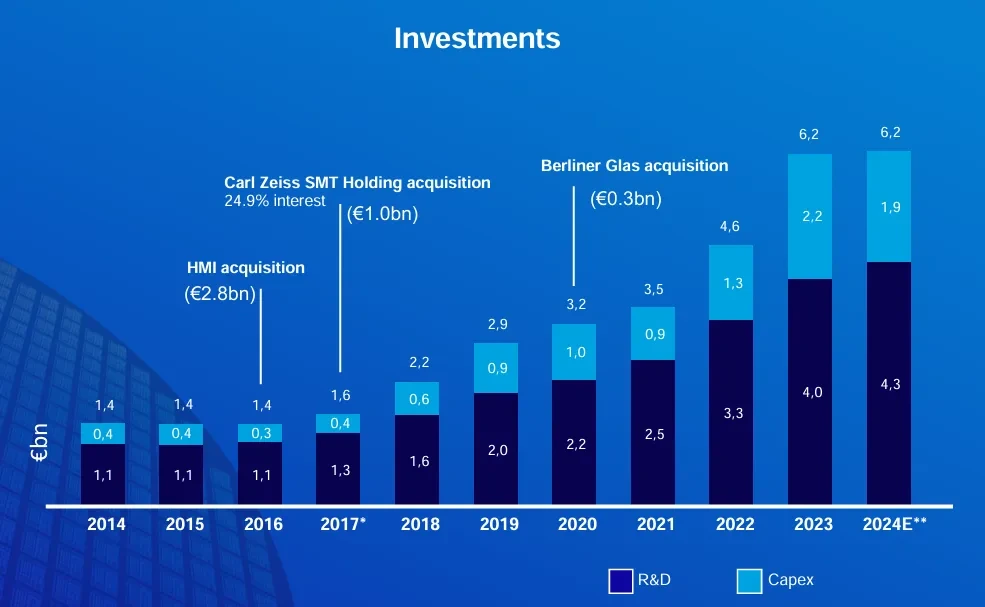

서문에 따르면 ASML의 기술 리더십은 고객에게 비용 효율적인 혁신을 제공하는 R&D 및 자본 지출에 대한 투자를 통해 유기적 성장을 달성하기 위한 전략적 투자에서 비롯됩니다.

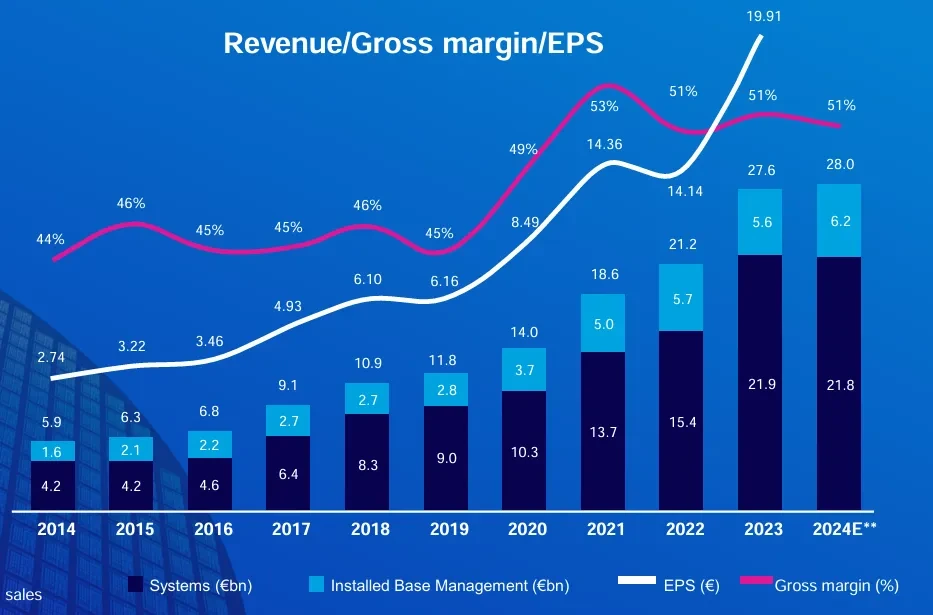

2014년 이후 ASML은 매출 성장, 마진 개선 및 자사주 매입에 힘입어 연평균 22%의 성장률을 기록했습니다. 강력한 성장 동력은 다음에서 비롯됩니다.

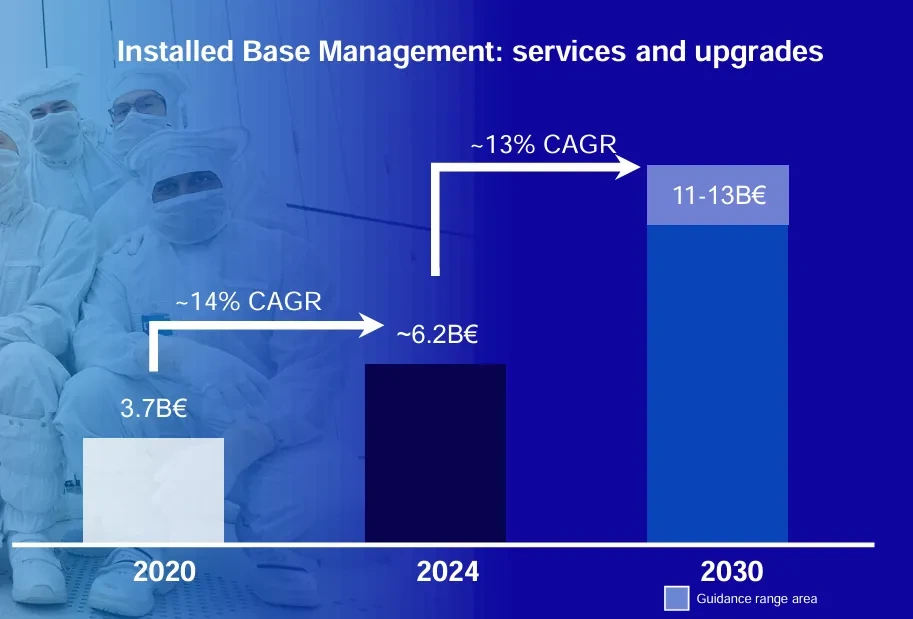

2014년 이후 시스템 수익은 18%의 CAGR로 성장했습니다. 설치된 업그레이드 및 서비스의 성장에 힘입어 Installed Base Management는 2014년 이후 14%의 CAGR로 성장했습니다. 매출총이익률은 2014년 44%에서 50% 이상으로 증가했는데, 이는 주로 EUV 수익성 개선에 기인합니다. 동시에 우리는 다른 사업에서 강력한 마진을 유지했습니다. 2014년 이후 주당순이익(EPS)은 수익성과 자사주 매입에 힘입어 연평균 22% 성장했습니다.

동시에 ASML은 2010-2024년 기간 동안 반도체 지수와 나스닥 기술 성장 지수를 능가하는 성과를 거두며 주주들에게 상당한 가치를 창출했습니다.

현재의 최종 시장, 웨이퍼 수요 및 리소(Litho) 지출이 증가함에 따라 ASML의 설치 인프라 사업의 성장을 계속 주도할 것입니다.

일부 데이터에 따르면 반도체 판매는 연평균 9%(2025-2030년)의 성장률로 성장하고 2030년까지 1조 달러를 초과할 것으로 예상됩니다. 서버, 데이터 센터 및 스토리지의 상당한 성장은 다른 영역의 속도 저하를 상쇄합니다.

웨이퍼 용량은 웨이퍼 수요와 전략적 고려 사항의 조합에 의해 주도될 것입니다.

전략적 고려 사항:

- 기술 주권은 국가의 목표가 팹 풋프린트를 (재)획득하는 것이기 때문에 설치된 용량의 덜 효율적인 사용으로 이어집니다.

- 공급 보안에 대한 강조가 증가함에 따라 소유권 분배의 지리적 다각화가 이루어졌으며, 이로 인해 로드 밸런싱이 더욱 어려워졌습니다.

- 경쟁이 치열해지면 플레이어가 시장 점유율을 확보하려고 할 때 과잉 생산 능력 기간이 발생할 수 있습니다.

그 결과, ASML은 수요 중심의 새로운 용량 외에도 2030년까지 전체 용량이 5-8% 증가할 것으로 예상합니다.

또한 고급 로직 및 DRAM의 점진적인 진화는 더 많은 계층과 지출을 주도할 것으로 예상됩니다. 웨이퍼 생산량 증가와 결합된 노출 증가는 EUV 지출의 연평균 성장률이 두 자릿수로 나타난다는 것을 의미합니다.

시장, 기술 및 리소그래피 프로세스의 시너지 개발 추세에 따라 포괄적인 분석을 통해 리소그래피 시장은 계속 발전하고 있으며 특정 점유율 및 변화는 다음 그림에 나와 있습니다.

- 시장 성장:Advanced Logic, DRAM 및 NAND 시장의 CAGR은 향후 몇 년 동안 높은 수준을 유지할 것으로 예상됩니다.

- 기술 개발: 모든 분야에서 고성능 및 저전력 설계가 발전하고 있으며, 생산성을 높이기 위해 EUV 노출 횟수를 늘리고 있습니다.

- 리소그래피 비용:첨단 공정 개발을 지원하기 위해 EUV 리소그래피 기술에 대한 투자는 계속 증가할 것입니다.

이 과정에서 증가하는 설치 기반은 서비스 및 확장성을 위해 설계되며, 현장 성능 업그레이드를 지원하면 두 자릿수 성장의 기회도 얻을 수 있습니다.

그 결과, ASML은 2030년까지 총 매출이 440억 유로에서 600억 유로 사이가 될 것으로 예상하고 있으며, 이는 주로 로직 및 메모리 칩에 의해 주도될 것으로 예상합니다. 다음 차트는 판매 기회 및 세그먼트의 성장 공간을 보여줍니다.

매출이 크게 증가했지만, 2025 회계연도부터 2030 회계연도까지 ASML의 매출총이익률 발전 잠재력은 엄청납니다.

- EUV: 0.33 NA 시스템의 생산 증가와 생산성 향상은 전체 GM(총 이익률)에 긍정적인 영향을 미쳤습니다. 0.55 NA 시스템의 수율 증가는 전체 GM에 대한 약간의 희석 효과를 가졌습니다.

- Non-EUV: GM의 성장은 주로 물량 성장에 의해 주도되었습니다. GM의 이러한 긍정적 효과는 제품 믹스의 변화(더 많은 DUV 건조 시스템)로 인해 부분적으로 상쇄되었습니다.

- IBM: GM은 설치 기반의 성장과 보다 가치 기반 서비스 및 업그레이드로의 전환으로 인해 증가했습니다.

위의 분석을 바탕으로 ASML은 다음과 같이 재무 기대치를 업데이트했습니다.

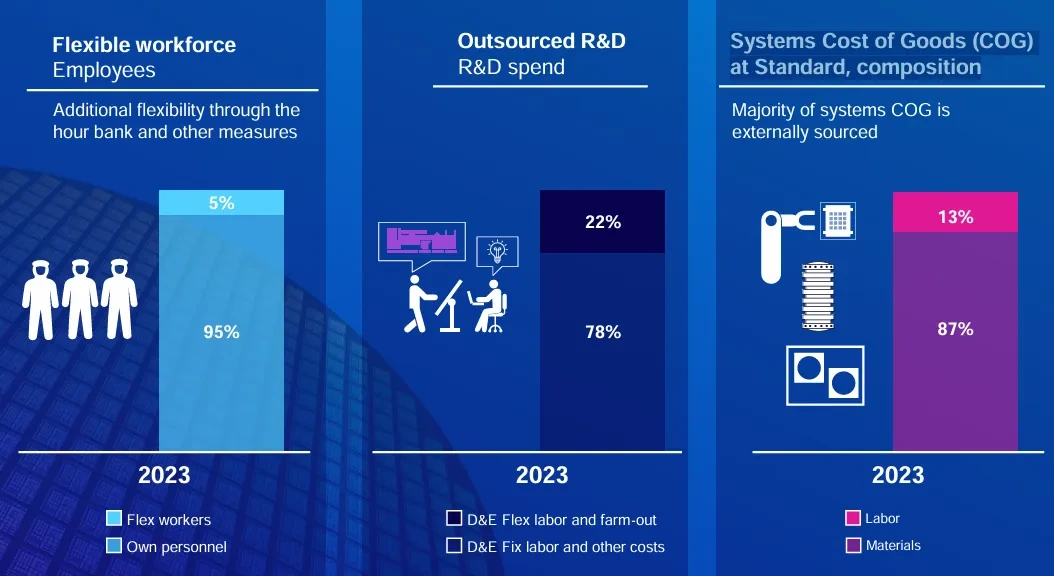

동시에 ASML은 업계의 변동성과 불확실성에 직면하여 유연한 인력, R&D 아웃소싱, 표준 기반 시스템 COG(Cost of Goods) 등 운영 모델에서 유연하게 대응하기 위해 노력해 왔습니다.

또한 주주를 위한 지속적인 가치 창출 측면에서. ASML은 강력하고 유연한 대차대조표가 뒷받침되는 자본 배분 및 자금 조달 방식을 통해 자체 비즈니스 투자에 중점을 둡니다.

자본 배분: ASML의 장기 로드맵에 투자하고 R&D 및 자본 지출을 통해 자체 사업에 투자하는 데 집중합니다. 주주 현금 수익(지속 가능한 주당 배당금은 시간이 지남에 따라 증가하며 분기별로 지급됩니다. 자사주 매입을 통한 초과 현금을 주주에게 반환).

자금 조달: 지속적인 비즈니스 성장을 보장하고 현금 흐름 변동에 대한 완충 장치를 제공할 수 있도록 충분한 유동성을 유지합니다. 탄탄한 투자등급 신용등급을 목표로 하는 자본 구조를 유지합니다.

행사 말미에 ASML의 사장 겸 CEO인 크리스토프 푸크(Christophe Fouque)는 ASML 투자자의 날의 하이라이트를 다음과 같이 요약했습니다.

- 반도체 산업은 여전히 강세를 유지하고 있으며, 슈퍼컴퓨터에 대한 막대한 투자와 업계 전체가 미래의 모든 주요 애플리케이션에 AI를 적용할 준비를 함에 따라 AI는 더 많은 기회를 창출할 준비가 되어 있습니다.

- 우리 업계는 AI의 예상 비용 및 전력 문제를 해결하기 위해 상당한 혁신이 필요하며, 이는 포트폴리오를 고급 로직 및 DRAM 전환으로 전환하기 위한 업계 로드맵을 더욱 주도할 것입니다.

- 우리의 고객들은 여전히 우리 전략의 중심에 있으며, 우리는 리소그래피가 계속해서 그들의 혁신의 중심에 있을 것이라고 믿습니다." 우리는 또한 고급 로직 및 메모리 공정에서 중요한 리소그래피 노출 수의 증가가 고객이 문제를 해결하는 데 계속 도움이 될 것으로 예상합니다."

- 우리는 우리의 능력이 1) EUV 기술을 향후 10년으로 확장할 것으로 예상합니다. 2) 3D 프런트 엔드 통합을 지원하기 위해 전체 리소그래피를 확장합니다. 3) DUV 제품의 성능과 비용 효율성을 개선하고 유연하고 다양한 제품 포트폴리오로 모든 고객의 요구를 지속적으로 충족시킵니다.

- 우리는 20년 수명 주기 동안 고부가가치 서비스와 업그레이드를 제공하기 위해 대규모로 성장하는 시스템 설치 기반(DUV, EUV)을 계속 활용할 것입니다.

- ASML은 강력한 업계 파트너십을 소중히 여기며, 이는 우리의 성공과 ESG 분야에서의 리더십에 대한 집단적 헌신에 매우 중요합니다.

- 반도체 산업의 장기 전망은 반도체가 여러 메가트렌드에서 수행하는 미션 크리티컬 조력자 역할을 고려할 때 여전히 유망합니다. 그 결과, 글로벌 반도체 매출은 연평균 9%(2025-2030년)로 성장하여 2030년까지 1조 달러를 초과할 것으로 예상됩니다.

- 이는 2025-2030년 기간 동안 매월 78,000개의 웨이퍼가 증가한 것입니다. AI가 선도적인 터미널 동인으로 부상한 것은 리소그래피 지출 관점에서도 웨이퍼 수요 패턴의 긍정적인 변화를 나타냅니다.

- 전략적으로 우리는 수요 주도 용량 추가 외에도 2030년까지 총 웨이퍼 용량이 5-8% 증가할 것으로 예상합니다.

- 우리는 고급 로직 및 DRAM의 개발이 더 많은 EUV 리소그래피 레이어와 지출을 주도할 것으로 기대합니다. 고급 로직의 경우 EUV Litho 지출이 10-20%의 CAGR로 증가할 것으로 예상합니다. DRAM의 경우 EUV 리소그래피 지출이 CAGR 15-25%로 성장할 것으로 예상됩니다.

- 반도체 최종 시장의 예상 성장과 미래 노드 리소그래피 지출의 증가는 당사 제품 및 서비스에 대한 수요를 주도하고 있습니다.

- 시장 및 리소그래피 시나리오에 따라 2030년까지 약 440억 유로에서 600억 유로의 연간 매출을 달성하고 총 마진은 약 56%에서 60%에 이를 수 있는 기회를 보고 있습니다.

- 우리는 배당금 증가와 자사주 매입의 조합을 통해 주주들에게 상당한 현금을 계속 환원할 것으로 기대합니다.

'Semiconductor' 카테고리의 다른 글

| SK실트론 : 미국 5억 4,400만 달러 대출 => 8인치 양산 (1) | 2024.11.19 |

|---|---|

| Tower Semiconductor - 3억 5천만 달러 투자 !!! - 반도체 (1) | 2024.11.19 |

| Microchip : CEO Ganesh Moorthy 사임 (2) | 2024.11.19 |

| 광동 주하이 - 100억 위안 : 실리콘 카바이드 관련 프로젝트 개시 !!! (0) | 2024.11.19 |

| Bejing - Big FAB - 반도체 : 12인치 !!! (1) | 2024.11.19 |

댓글