01 에칭이란?

최신 실리콘 칩은 수백만 또는 수십억 개의 트랜지스터(전기 신호와 전력을 전환하는 전자 장치의 기본 구성 요소) 및 기타 유형의 장치를 통해 전기를 전도할 수 있는 복잡한 회로 패턴을 가지고 있으며, 그 중 일부는 실리콘 원자 너비가 수십 개에 불과합니다.

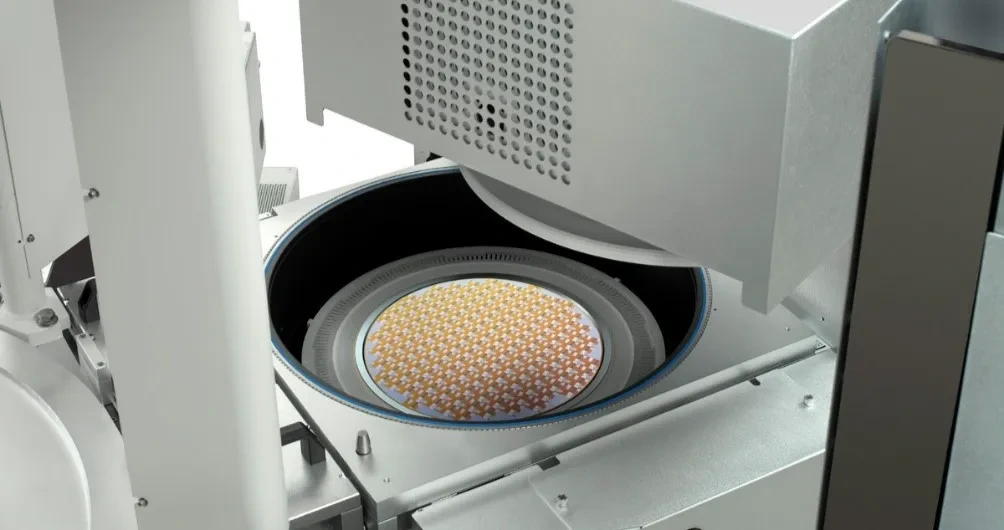

이러한 회로 패턴을 만들려면 실리콘 및 기타 재료를 웨이퍼 표면에서 정밀하게 제거하여 경로를 형성해야 합니다. 이 과정을 계속해서 반복하여 다층 회로를 만듭니다.

에칭은 웨이퍼 표면에서 재료를 제거하여 특정 깊이와 모양의 구조를 만드는 제조 공정입니다.

02 에칭 부문

반도체 제조에는 두 가지 주요 유형의 에칭이 있습니다.

습식 에칭

습식 에칭은 웨이퍼에서 물질을 제거하기 위해 화학 반응에 의존하여 웨이퍼를 에칭하기 위해 에칭 화학 물질을 포함하는 용액을 사용하는 것으로, 일반적으로 등방성, 즉 에칭 속도는 수직 및 수평 방향 모두에서 동일합니다.

► 습식 에칭은 선택성이 높지만 에칭 후 구조의 최종 모양을 제어하는 방법이 제한적입니다. 동시에 습식 에칭에는 종종 건조 단계가 필요하며, 이는 패턴 붕괴의 위험을 증가시킵니다.

드라이 에칭

고급 공정 기술은 웨이퍼에 이상적인 패턴과 모양을 형성하기 위해 건식 에칭을 사용하는 것을 선호합니다. 건식 에칭은 가스를 사용하며 일반적으로 진공 상태에서 수행되며 에칭 부산물은 휘발성이 높아 추출할 수 있습니다.

► 플라즈마는 일반적으로 건식 에칭에 사용되어 기체 식각액을 해리하여 더 많은 화학 활성 종(자유 라디칼)을 생성하고 이온화 가스를 생성하여 이온을 생성합니다. 이온은 웨이퍼 표면에 충격을 가하고 FinFET(FinFET) 및 GAA(서라운드 게이트 장치)의 형성에 중요한 이방성 특성을 나타냅니다.

저온 에칭 공정은 20 세기의 80 년대에 처음 개발되었으며 현재 건식 에칭 방법 중 하나로 다시 부상하고 있습니다. 이 공정은 더 낮은 웨이퍼 온도(일반적으로 0°C 미만)에서 수행되며 온도 제어 장치는 더 낮은 온도에서 작동합니다. 저온 에칭은 횡방향 에칭 속도를 제어하면서 활성 물질의 흡착을 향상시키는 데 도움이 됩니다.

► 일부 높은 종횡비 에칭 응용 분야에서, 새로운 에칭 화학 및 고급 RF 펄스와 결합된 저온 에칭은 더 빠른 에칭 속도와 더 쉬운 방향성 제어를 가능하게 합니다.

03 에칭 장비 유형

이제 에칭의 기초를 이해했으므로 다음 단계는 이러한 작업을 수행하는 장비입니다. 전통적으로 에칭 장비는 도체 에칭 장비와 유전체 에칭 장비로 나뉩니다. FinFET, GAA와 같은 새로운 기술 변곡점의 출현으로 선택적 에칭은 제3의 에칭 장비로 부상하고 있습니다.

지휘자 에칭:

도체 에칭은 일반적으로 실리콘, 게르마늄, 실리콘 게르마늄, 금속, 탄소 및 이산화규소/질화규소와 같은 얇은 유전층을 에칭합니다. 이 장치는 유도 결합 플라즈마를 사용하며 일반적으로 높은 이온 밀도 공정에서 작동합니다.

유전체 에칭:

유전체 에칭은 일반적으로 두꺼운 유전체 필름(이산화규소 및 질화규소)을 에칭하며 다른 재료에 대한 선택성이 높습니다. 이 장치는 용량성 결합 플라즈마를 사용하며 일반적으로 낮은 플라즈마 밀도 공정에서 고에너지 이온으로 작동합니다.

선택적 에칭:

선택적 에칭은 인접 재료를 수정하거나 손상시키지 않고 웨이퍼 표면에서 재료를 정밀하게 제거합니다. 플라즈마의 사용은 선택 비율과 식각 속도 요구 사항에 따라 다릅니다.

04 에칭 메커니즘

에칭은 두 가지 기본 메커니즘을 통해 재료를 제거합니다.

물리적 메커니즘 :

충분한 에너지를 가진 이온은 물질에서 원자를 제거하며, 이 과정은 스퍼터링이라고도 합니다. 스퍼터링된 원자는 휘발성이 낮을 수 있고, 표면의 나머지 부분(예를 들어, 에칭 측벽)에 증착될 수 있다.

화학:

에칭트(자유 라디칼)는 웨이퍼 표면의 원자와 화학 결합을 형성하고 표면을 기체로 남깁니다. 예를 들어, 4개의 불소 원자가 1개의 실리콘 원자와 결합하여 웨이퍼 표면을 떠나는 사불화규소(SiF4) 가스를 형성할 수 있습니다. 그러나 화학 반응이 일어나기 위해서는 반응 활성화 에너지가 필요하며, 이는 일반적으로 열에 의해 제공됩니다. 저온 에칭은 화학적 에칭을 억제하여 더 나은 에칭된 측벽 프로파일을 만듭니다.

더 발전된 에칭 메커니즘:

이온 중립 시너지:

램리서치(Lam Research)의 전 최고기술책임자(CTO)인 릭 고트초(Rick Gottscho)가 만든 용어입니다. 플라즈마 에칭에서 물리적 에칭과 화학적 에칭은 서로를 보완하며 동시에 수행됩니다. 이온은 화학 반응이 일어나는 데 도움이 되는 반응 활성화 에너지를 제공하는 반면, 화학 성분은 휘발성 에칭 부산물이 형성되고 펌핑되도록 합니다. 물리적 또는 화학적 에칭만 하는 것에 비해 이온 중성 시너지 효과를 내는 플라즈마 에칭은 더 빠르며 선택 비율과 에칭 측벽 프로파일을 더 잘 제어할 수 있습니다.

원자층 에칭:

웨이퍼의 최상부 원자층에서 자기 제한 화학 반응(흡착)이 발생하고 재료의 최상층이 변형됩니다. 그 후, 개질된 층은 이온 또는 다른 에칭제로 활성화되어 휘발성 부산물을 형성하고, 이는 표면에서 제거(탈착)되고 제거됩니다. 흡착 및 탈착 단계는 플라즈마를 사용하거나 사용하지 않고 설계할 수 있습니다.

용어집

1. 흡착은 기체 또는 액체의 분자 또는 원자가 고체 물질의 표면에 흡착되는 과정을 말합니다.

2. 깊이 대 너비 비율은 구조물의 깊이와 너비의 비율을 나타냅니다. 높이 대 종횡비 구조는 일반적으로 매우 높으며 상단에 작은 구멍이 있습니다.

3. 용량성 결합 플라즈마는 진공 챔버에서 두 개의 평행한 전극 사이에서 생성되는 플라즈마 유형입니다.

4. 방향성(directionality)은 특정 방향으로 나타나거나, 있거나, 흐르는 것의 속성 또는 특성을 말합니다.

5. 해리는 분자 결합을 자유 라디칼이라고도 하는 더 작고 더 활동적인 구성 요소로 분해하는 것을 말합니다.

6. 에칭 부산물은 에칭 공정에서 형성되는 2차 생성물이며 휘발성인 경우 추출할 수 있습니다.

7. 에칭 속도는 에칭 공정에서 재료가 제거되는 속도를 나타냅니다.

8. FinFET(FinFET)는 최신 프로세서 설계에 사용되는 비평면 또는 3D 트랜지스터입니다.

9. 유도 결합 플라즈마는 전자기 유도에 의해 생성된 전류에 의해 에너지가 제공되는 플라즈마 소스입니다.

10. 패턴 붕괴는 포토레지스트 층이 구부러지거나 기계적으로 불안정하게 만들어 후속 패턴 전송 단계에서 패턴화된 형상을 사용할 수 없게 만드는 힘입니다.

11. 자유 라디칼은 플라즈마 에칭 공정에서 화학 반응에 관여하는 반응성이 높은 화학 물질로 재료 제거 및 표면 개질을 돕습니다.

12. RF 펄스는 무선 주파수 에너지를 연속적이지 않고 펄스로 변조하는 기술을 말합니다.

13. 선택 비율은 에칭 공정에서 두 재료 간의 에칭 속도 차이를 나타냅니다.

14. 휘발성은 물질이 공칭 온도에서 증발하는 경향을 나타냅니다.

웨이퍼를 반도체로 만드는 데는 수백 가지 공정이 있습니다. 가장 중요한 공정 중 하나는 웨이퍼에 새겨진 섬세한 회로 패턴인 에칭(Etch)입니다. 에칭 프로젝트의 성공 여부는 정의된 분포 내에서 다양한 변수를 관리하고 각 에칭 장비가 최적의 조건에서 작동할 수 있도록 준비되는 데 달려 있습니다. 당사의 에칭 공정 엔지니어는 정교한 제조 기술을 사용하여 이 세부 사항을 완성합니다.

SK하이닉스 프레스센터는 이천 D램 Front Etch(Etched), Middle Etch, End Etch 기술팀 관계자들을 인터뷰해 이들의 작업에 대해 자세히 알아봤다.

Etch: 생산성 향상을 위한 여정

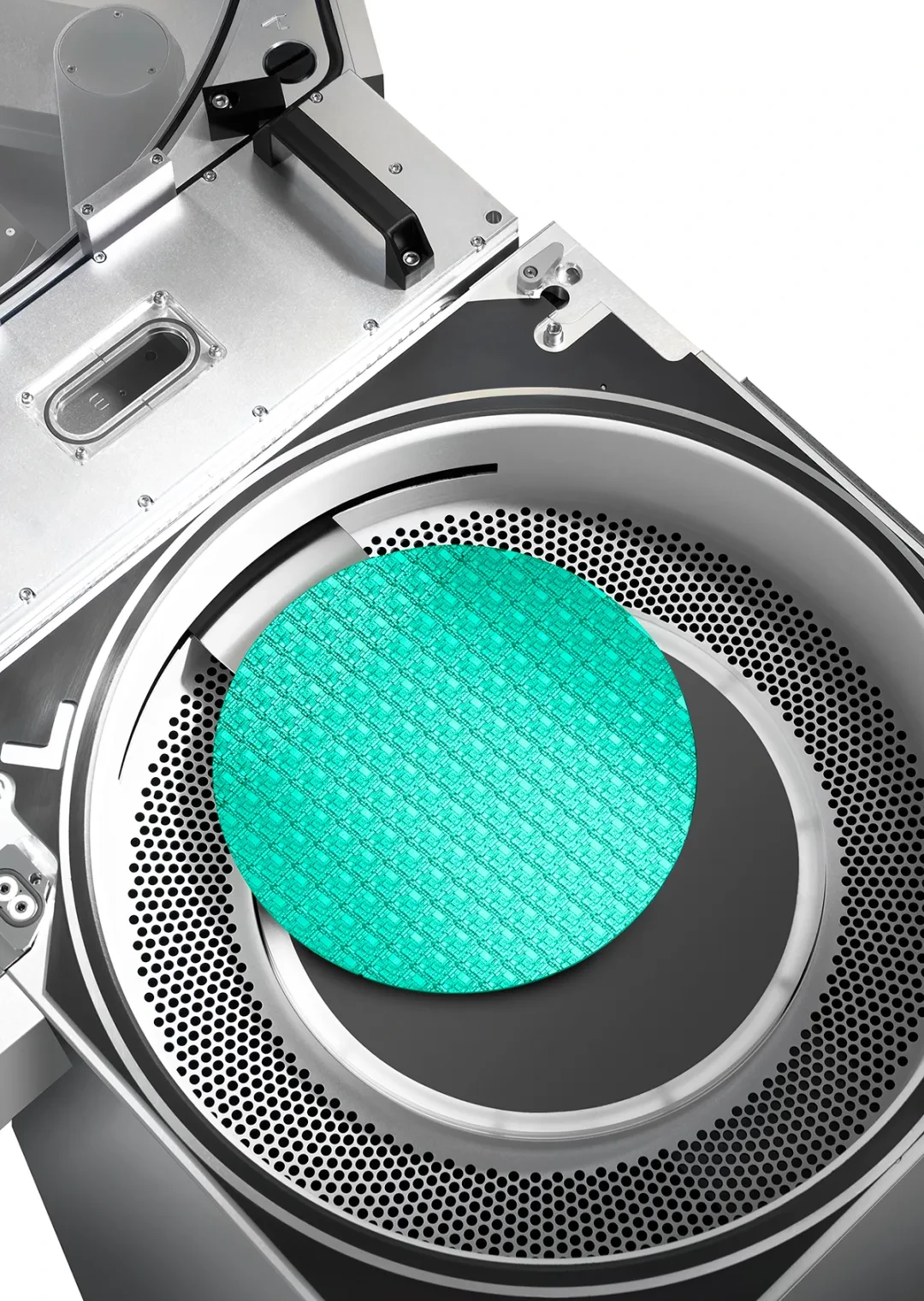

반도체 제조에서 에칭은 박막에 패턴을 조각하는 것을 말합니다. 패턴은 플라즈마를 사용하여 분무되어 각 공정 단계의 최종 윤곽을 형성합니다. 주요 목표는 레이아웃에 따라 정확한 패턴을 완벽하게 제시하고 모든 조건에서 균일하고 일관된 결과를 제공하는 것입니다.

증착 또는 포토리소그래피 프로젝트에서 문제가 발생하면 선택적 에칭으로 해결할 수 있습니다. 그러나 에칭 과정에서 문제가 발생하면 상황을 되돌릴 수 없습니다. 조각 영역을 동일한 재료로 채울 수 없기 때문입니다. 따라서 반도체 제조 공정에서 에칭은 전체 수율과 제품 품질을 결정하는 데 중요합니다.

에칭 공정은 ISO, BG, BLC, GBL, SNC, M0, SN 및 MLM의 8단계로 구성됩니다.

먼저, ISO(Isolation) 스테이지는 웨이퍼에 실리콘(Si) 에칭(Etch)을 수행하여 활성 셀 영역을 생성합니다. BG(Buried Gate) 단계에서는 워드라인1과 게이트를 형성하여 전자 채널을 생성한다. 그런 다음 BLC(Bit Line Contact) 단계는 셀 영역 내에서 ISO와 비트 라인 2 간의 연결을 생성합니다. GBL(Peri Gate+Cell Bit Line) 단계에서는 셀 열 주소 라인과 Peri 3의 게이트가 동시에 생성됩니다.

SNC(Storage Node Contract) 단계에서는 활성 영역과 스토리지 노드 4 간의 연결이 생성됩니다. 이어서, M0(Metal0) 위상은 주변 S/D(Storage Node)5의 접속점과 컬럼 어드레스 라인과 스토리지 노드 사이의 접속점을 형성한다.

SN(Storage Node) 스테이지에서 셀 용량을 확인한 후 MLM(Multi Layer Metal) 스테이지에서 외부 전원 공급 장치 및 내부 배선을 생성하고 전체 Etch 엔지니어링 프로세스가 완료됩니다.

에칭 기술자는 주로 반도체 패터닝을 담당하기 때문에 DRAM 사업부는 세 팀으로 나뉩니다. 미들 에칭 (에칭) (GBL, SNC, M0); 엔드 에칭(SN, MLM). 이 팀은 또한 제조 및 장비 직책으로 나뉩니다.

제조 직책은 셀 생산 공정을 관리하고 개선하는 일을 담당합니다. 제조 위치는 수율과 제품 품질을 개선하기 위해 가변 제어 및 기타 생산 최적화 조치를 사용하기 때문에 중요합니다.

장비 위치는 에칭 공정 중에 발생할 수 있는 문제를 방지하기 위해 생산 장비를 관리하고 강화하는 일을 담당합니다. 장비 위치의 핵심 책임은 장비의 최상의 성능을 보장하는 것입니다.

명확한 책임에도 불구하고 모든 팀은 생산 프로세스 및 관련 장비를 관리하고 개선하여 생산성을 높인다는 공통의 목표를 향해 노력합니다. 이를 위해 각 팀은 각자의 성과와 개선점을 적극적으로 공유하고, 사업 성과 향상을 위해 협력한다.

소형화 기술의 과제를 해결하는 방법

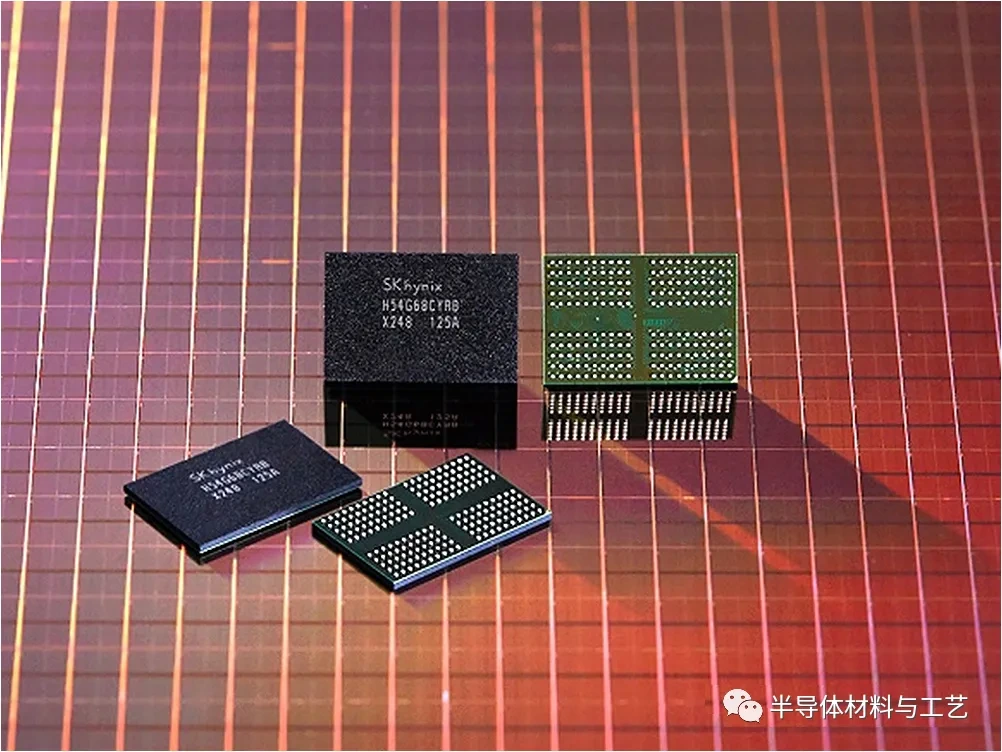

SK하이닉스는 2021년 7월 10나노(1a) 공정용 8Gb LPDDR4 D램 제품 양산을 시작했습니다.

반도체 메모리 회로 패턴은 10nm 시대에 접어들었으며, 단일 DRAM에 약 10,000개의 셀을 수용할 수 있도록 개선되었습니다. 결과적으로 에칭 공정 중에도 공정 마진이 부족합니다.

홀6의 형성이 너무 작으면 "열리지 않음" 상태로 나타나 칩의 하부를 막을 수 있습니다. 또한, 형성된 구멍이 너무 크면 "브리징" 현상이 발생할 수 있습니다. 두 구멍 사이에 간격이 충분하지 않으면 "브리징" 현상이 발생하여 후속 단계에서 상호 접착 문제가 발생합니다. 반도체가 더욱 정교해짐에 따라 구멍 크기 값의 범위가 줄어들고 있으며 이러한 위험은 점차 제거될 것입니다.

이러한 문제를 해결하기 위해 에칭 전문가들은 공정 레시피 및 APC7 알고리즘을 수정하고 ADCC8 및 LSR9와 같은 새로운 에칭 기술을 도입하는 등 공정을 지속적으로 개선하고 있습니다.

고객의 요구가 더욱 다양해짐에 따라 또 다른 과제가 발생하는데, 바로 다중 제품 생산 추세입니다. 이러한 고객 요구 사항을 충족하기 위해서는 각 제품에 대한 최적의 공정 조건을 개별적으로 설정해야 합니다. 이는 엔지니어에게 매우 특별한 과제인데, 이는 생산 기술이 기존 조건과 다양한 조건의 요구 사항을 모두 충족하도록 해야 하기 때문입니다.

이를 위해 에칭 엔지니어들은 핵심 제품을 기반으로 다양한 파생 상품을 관리하는 "APC offset"10 기술을 도입함과 동시에 각 제품을 종합적으로 관리하기 위해 "T-index 시스템"을 구축 및 활용했습니다. 이러한 노력의 결과로, 시스템은 다중 제품 생산의 요구를 충족시키기 위해 지속적으로 개선되었습니다.

'Semiconductor' 카테고리의 다른 글

| 주성엔지니어링 - 최신 원자층 증착(ALD) 기술 개발에 성공 (0) | 2024.07.19 |

|---|---|

| 삼성 전자, SK Hynix - 전략 !!! (0) | 2024.07.17 |

| CPU 생산 공정 - 기본 다이어그램 (1) | 2024.07.17 |

| DRAM - 새로운 경쟁 개시 !!! (1) | 2024.07.17 |

| HBM 새로운 경쟁 개시 !!! (0) | 2024.07.17 |

댓글