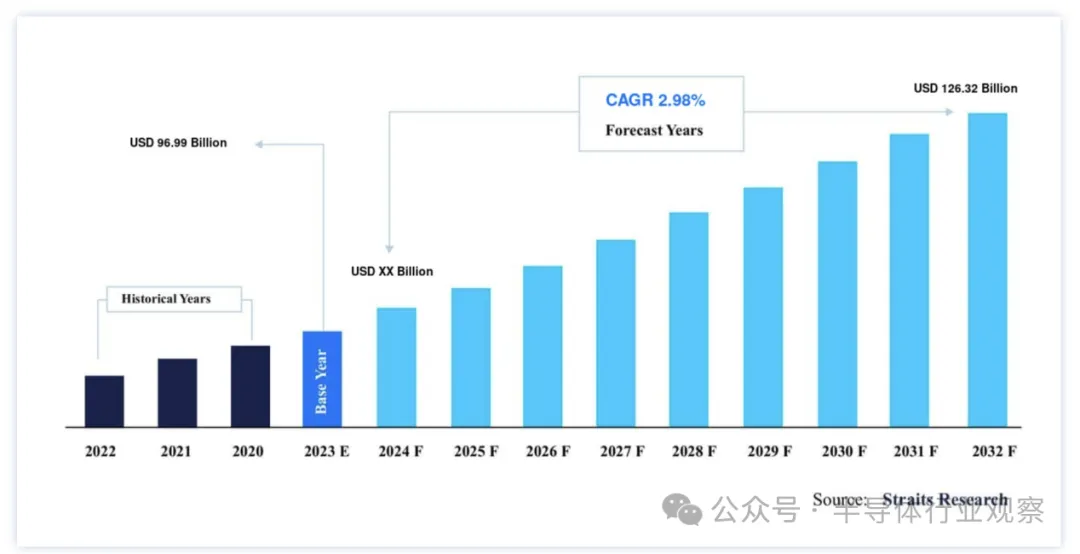

반도체 시장에서 가장 큰 부문 중 하나인 DRAM의 영향력은 자명합니다. 스트레이츠 리서치(Straits Research)에 따르면 2022년 글로벌 동적 랜덤 액세스 메모리(DRAM) 시장 규모는 969억 9천만 달러로 평가되었습니다. 2031년까지 1,263억 2,000만 달러에 이를 것으로 예상되며 예측 기간(2023-2031) 동안 2.98%의 CAGR을 등록할 것으로 예상됩니다

스트레이츠 리서치는 DRAM이 향후 급속한 발전을 이룰 수 있는 이유는 노트북/태블릿, 스마트폰, 디지털 카메라 등 가전제품 판매의 꾸준한 성장과 더불어 클라우드 컴퓨팅, 인공지능, 사물인터넷 등 메가트렌드의 지속적인 발전이 장기적으로 DRAM을 낙관할 수 있는 핵심 요인이기 때문이라고 본다.

그러나 단말 수요를 자세히 살펴보면 인공 지능이 주도하는 HBM이 향후 DRAM의 발전에 중요한 동력원이 될 것임을 알 수 있습니다. 시장 분석업체 트렌드포스(TrendForce)는 지난 5월 전체 DRAM 비트 용량에서 HBM이 차지하는 비중이 2023년 2%에서 2024년 5%, 2025년 10% 이상으로 증가할 것으로 예상된다고 밝혔다. 가치 측면에서 HBM은 2024년부터 전체 D램 시장 가치의 20% 이상을 차지할 것으로 예상되며, 2025년에는 30% 이상을 차지할 것으로 예상됩니다.

하지만 사실 HBM 외에도 삼성전자, SK하이닉스, 마이크론 등 D램 거물들이 D램의 미래 기회를 놓치지 않기 위해 다방면으로 노력하고 있다.

HBM, 심화

HBM은 전 세계적으로 주목을 받고 있으며, 이전 기사 "HBM 4, 거의 완성 직전"에서 빅 3 경쟁의 다음 단계를 공개했습니다. 하지만 그 전에도 HBM3e를 차지하기 위한 경쟁은 한창 진행 중이었습니다.

삼성전자는 올해 2월 최대 용량 36GB의 HBM3E 12단 고대역폭 메모리(HBM)를 최초로 선보이며 반도체 업계에 큰 도약을 이뤘다. 16일 업계 관계자에 따르면 삼성전자는 5세대 HBM 제품의 2분기 양산을 시작해 현재 일부 고객사에 공급하고 있다.

TSV(through-silicon via) 기술을 적용해 최대 12겹까지 쌓이는 HBM3E 12단 적층 D램 메모리 칩이 올해 하반기 AI 반도체 시장의 핵심 전장이 되고 있다. 이러한 발전은 삼성전자, SK하이닉스, 마이크론이 모두 주도권을 놓고 경쟁하는 메모리 기업들 간의 경쟁을 심화시켰습니다.

삼성전자는 하반기 엔비디아에 HBM3E 12레이어 제품을 공급하기 위해 퀄리티 테스트를 통과해야 한다. 성공적인 대량 생산에도 불구하고 품질 테스트를 통과하지 못하면 사전 생산 제품의 재고가 적체될 수 있습니다. 결과적으로 삼성은 NVIDIA의 표준을 충족하기 위해 최선을 다하고 있습니다.

SK하이닉스도 3분기 HBM3E 12단 양산을 준비 중이다. 현재 NVIDIA에 이전 HBM3E 8 레이어를 공급하고 있지만 12 레이어 버전에 대한 품질 테스트 요청은 아직 받지 못했습니다. SK하이닉스는 양산 일정을 내년에서 3분기로 앞당기며 시장 리더십에 박차를 가하고 있다.

마이크론은 이번 경쟁에서 다크호스로 꼽히며 하반기 HBM3E 12레이어 양산 준비를 완료하고 내년 엔비디아 등 주요 고객사에 공급할 계획이다. 아직 엔비디아에 HBM3E 12티어를 공급하기로 결정한 메모리 업체가 없기 때문에 마이크론은 수요를 충족하고 유리한 가격을 보장하기 위해 세 회사 모두의 제안을 동시에 고려할 가능성이 높습니다.

업계 관계자는 "경쟁 심화로 HBM3E 12층의 가격이 소폭 하락할 수 있지만, 하반기는 HBM의 시장 구조를 결정할 시기임이 분명하다"고 말했다. "관건은 각 기업이 얼마나 수익률을 높일 수 있느냐 하는 것입니다." ”

올해 하반기는 HBM 시장의 미래를 결정하는 중요한 시기가 될 것입니다. HBM3E 12레이어 제품을 누가 먼저 엔비디아에 공급하느냐에 따라 SK하이닉스가 HBM의 선두 자리를 지킬 수 있을지, 아니면 삼성전자가 전세를 뒤집을 수 있을지가 결정된다. HBM3E 12번째 티어의 선두 자리를 확보하는 것은 각 회사의 시장 지위와 재무 건전성에 상당한 영향을 미칠 수 있기 때문에 경쟁이 치열하고 위험성이 높습니다.

LPDDR은 계속 뜨겁습니다.

한국 매체 조선이 전한 것처럼 한때 속도와 용량에 중점을 두었던 반도체 산업은 이제 전력 효율성으로 전환되고 있습니다. AI 학습과 훈련이 고도화됨에 따라 방대한 양의 데이터를 처리하는 데 필요한 전력도 급격히 증가하여 저전력 칩 개발 경쟁이 심화되고 있습니다.

인공 지능 칩은 종종 "대규모 에너지 소비자"라고 불리며 전기를 많이 소비합니다. NVIDIA의 곧 출시될 고성능 AI 칩인 B100에는 1000와트의 전력이 필요합니다. 이전 AI 칩 모델인 A100과 H100은 각각 400와트와 700와트가 필요했기 때문에 성능이 높을수록 전력 소비가 커졌습니다.

AI 칩용 메모리 칩을 공급하는 대표적인 칩 제조업체인 삼성전자와 SK하이닉스가 새로운 저전력 반도체 솔루션을 출시합니다.

저전력 칩은 배터리 수명을 절약하면서 인터넷 연결 없이 AI 계산을 수행해야 하는 스마트폰, 태블릿 및 노트북과 같은 장치에 필수적입니다. 반도체 업계 관계자는 "저전력 반도체는 모바일 기기의 배터리 수명을 연장하고 서버 데이터 처리에 필요한 에너지의 양을 줄일 수 있다"고 말했다. "전력 공급이 부족해짐에 따라 저전력 반도체는 더욱 중요해질 것입니다."

LPDDR 또는 Low Power Double Data Rate Memory는 저전력 칩의 최전선에 있습니다. 단일 데이터 경로를 가진 기존 DRAM과 달리 DDR은 두 개의 경로를 가지고 있어 더 빠른 데이터 처리가 가능합니다. LPDDR은 또한 전력 소비를 줄이며 최대 Gen 7(5X)까지 개발되었습니다. 일반적으로 고성능 스마트폰 및 노트북에 사용됩니다.

삼성전자와 SK하이닉스 모두 LPDDR 연구개발에 박차를 가하고 있다. 올해 4월 삼성전자는 역대 가장 빠른 저전력 D램 칩인 LPDDR5X(7세대)를 개발했다. 이 회사는 최근 속도 검증을 완료하고 양산을 준비 중인 것으로 알려졌다. 이 신제품은 이전 세대보다 30% 이상 더 많은 용량을 제공하는 동시에 25% 더 적은 전력을 소비합니다. 이 회사는 성능과 속도에 따라 전력을 조정하는 새로운 기술을 채택했습니다.

SK하이닉스는 지난해 말 최초로 5배 향상된 성능을 선보인 LPDDR5T DRAM을 상용화했는데, 이 D램은 중국 스마트폰 제조사 비보의 플래그십 모델에 채택돼 1초에 15개의 Full HD 영상을 처리할 수 있는 동시에 전력 소모를 대폭 줄일 수 있다.

최근에는 LPDDR 적층 기술도 활발하게 개발되고 있습니다. 여러 DRAM이 적층된 HBM(고대역폭 메모리)과 마찬가지로 LPDDR 적층은 전력 소비를 최소화하면서 용량과 속도를 높이도록 설계되었습니다.

동시에 차세대 LPDDR6 표준도 추진되고 있습니다.

올해 3월 보도 자료에 따르면 국제반도체표준기구(JEDEC)는 리스본에서 열린 회의에서 LPDDR6 표준에 대한 광범위한 논의를 가졌다. 이 메시지는 새로운 LPDDR6 RAM이 최대 12,800MT/s의 데이터 속도를 달성할 수 있음을 보여줍니다.

LPDDR6 표준의 개발은 데이터 처리 성능 향상에 중점을 둘 것으로 예상됩니다. 스마트폰, 노트북, 태블릿의 대규모 AI 컴퓨팅에 대한 온디바이스 AI 수요가 급속히 증가함에 따라 메모리 성능의 중요성이 더욱 강조되고 있기 때문입니다. 또한 전력 소비 기준도 상향 조정될 것으로 알려졌다.

소식통은 "데이터 처리에 따라 증가하는 전력 소비를 최소화하는 방식으로 기술 개발과 표준 논의가 진행되고 있다"고 말했다. ”

각각 이상한 트릭을 가진 시장 세그먼트

표준 시장에 초점을 맞추는 것 외에도 이러한 주요 DRAM 제조업체는 각각 이상한 움직임을 보이는 시장 부문에도 주목하고 있습니다.

먼저 삼성전자를 살펴보면, 삼성전자가 애플의 차세대 XR 기기에 LLW D램을 공급하기 위한 기술을 개발 중인 것으로 파악된다. 업계 관계자에 따르면 삼성전자는 애플에 LLW D램을 공급하기 위한 제품을 개발 중이다.

LLW DRAM은 차세대 DRAM으로, 기존 모바일 제품인 LPDDR에 비해 입출력(I/O) 단자 수를 늘려 대역폭(데이터 송수신 경로)을 늘린 신기술이다. 이를 통해 128GB/s의 고성능 및 저지연 기능을 제공합니다. 이를 통해 디바이스 측 AI 산업에 적용되어 기존 LPDDR을 대체할 수 있을 것으로 기대된다.

애플도 LLW DRAM에 관심이 많은 것으로 알려졌다. 실제로 애플은 지난해 6월 SK하이닉스의 LLW D램을 도입해 최첨단 XR 기기인 비전프로를 출시한 바 있다. 관련 보도에 따르면 SK하이닉스는 R1의 고속 처리를 지원하기 위해 맞춤형 1기가비트 D램을 개발했다. 새로운 DRAM은 대기 시간을 최소화하기 위해 입력 및 출력 핀 수를 8배 늘렸다고 합니다. 이 칩은 대기 시간이 짧은 와이드 IO라고도 합니다. 전문가들에 따르면 새로운 칩은 R1 칩셋에 단일 장치로 연결된 특수 패키징 방법인 팬아웃 웨이퍼 레벨 패키징을 가지고 있는 것으로 보입니다.

앞서 언급했듯이 삼성전자도 애플에 LLW D램을 공급하기 위한 기술 개발을 지속하고 있는 것으로 파악됐다.

이 사안에 정통한 한 관계자는 "삼성전자가 애플로부터 2022년 LLW D램 공급 제안을 받은 것으로 알고 있다"며 "현재 소량 생산을 포함해 상용화 중"이라고 설명했다. 또 다른 관계자는 "삼성전자가 애플의 LLW D램 공급망에서 SK하이닉스를 따라잡기 위해 노력하고 있다"며 "특별한 메모리로 차세대 비전프로 등에 활용할 수 있다"고 말했다. ”

데이터 센터 시장에서 DRAM의 경우 제조업체도 칼을 보여주었습니다. 예를 들어, 서버 및 데이터 센터의 대역폭 수요에 대응하여 주요 DRAM 제조업체는 DRAM 속도를 DDR 5의 최대 속도 이상으로 높이기 위해 다양한 접근 방식을 취하고 있습니다. 2022년 말, SK하이닉스는 일부 인텔 서버 플랫폼을 위한 MCR-DIMM을 출시했습니다. MCR(Multiplexer Combo Class) DIMM으로 알려진 이 기술을 통해 하이엔드 서버 DIMM은 8Gbps의 낮은 데이터 속도로 작동할 수 있으므로 기존 DDR5 메모리 제품(4.8Gbps)에 비해 대역폭이 80% 증가합니다. MCR DIMM의 기술은 하나가 아닌 두 개의 랭크를 동시에 사용할 수 있기 때문에 흥미롭고, 기본적으로 두 세트/등급의 메모리 칩을 결합하여 유효 대역폭을 두 배로 늘립니다.

동시에 표준 기구인 JEDEC도 유사한 방식으로 MR-DIMM에 대한 사양을 개발했습니다. 모두 기존 DDR5 기술을 기반으로 하며 피크 대역폭과 대기 시간을 개선하기 위해 여러 계층을 결합하려고 시도합니다.

MR-DIMM 표준은 개념적으로 단순하며, 데이터 버퍼가 있는 표준 DDR5 속도로 실행되는 여러 메모리 모듈을 사용합니다. 버퍼는 호스트 인터페이스 측에서 2배속으로 실행되므로 전송 속도를 두 배로 높일 수 있습니다. 이 설계의 과제는 호스트 메모리 컨트롤러에서 로직을 더 빠른 속도로 실행하고 전력/열을 제어할 수 있다는 점도 분명합니다.

JEDEC MR-DIMM 표준의 첫 번째 버전은 8,800MT/s의 속도를 지정하고 다음 세대는 12,800MT/s의 속도를 지정합니다. JEDEC는 또한 DDR5 표준의 개선에 보조를 맞추기 위해 이 기술에 대한 명확한 로드맵을 제시했습니다.

지난 몇 분기 동안 Micron과 Intel은 전자의 1세대 MR-DIMM 시리즈를 시장에 출시하기 위해 긴밀히 협력해 왔습니다.

JEDEC 사양에서 알 수 있듯이 MR-DIMM의 장점은 대기 시간을 개선하면서 데이터 속도와 시스템 대역폭을 높일 수 있다는 것입니다. 용량 측면에서 Micron은 모듈의 열 수를 늘릴 수 있기 때문에 256GB의 용량을 제공할 수 있습니다. 일부 공급업체는 표준 DDR5 속도에서 패키지당 용량을 늘리기 위해 TSV(Through-Silicon Via) 기술을 사용하고 있지만 이로 인해 MR-DIMM 제조 공정에는 거의 없는 추가 비용과 복잡성이 추가된다는 점에 유의해야 합니다.

Micron은 MR-DIMM 샘플을 공개적으로 발표한 최초의 회사도 아닙니다. 삼성전자는 지난달 자체 제품 라인(16Gb DRAM 칩 기반)을 발표했다.

삼성전자는 서버 마더보드에 추가 메모리 슬롯 없이 더 많은 메모리와 대역폭을 제공하기 위해 다단계 버퍼링 듀얼 인라인 메모리 모듈(MRDIMM)을 개발했다고 밝혔다. 이 모듈은 두 개의 DDR5 구성 요소를 결합하여 기존 DRAM 구성 요소의 대역폭을 두 배로 늘려 최대 8.8Gb/s의 데이터 전송 속도를 제공합니다. MRDIMM은 데이터를 처리하고 복잡한 계산을 고속으로 수행하기 위해 고성능 컴퓨팅(HPC)이 필요한 AI 애플리케이션에 적극적으로 사용될 것으로 예상됩니다. 삼성전자는 현재 성능, 용량 및 전력 소비가 향상된 16Gb 모노 MRDIMM 장치를 샘플링하고 있다고 강조했습니다. 삼성전자는 이 혁신적인 메모리 솔루션을 통해 인공지능(AI), 머신러닝(ML), 대규모 언어 모델(LLM) 처리 분야의 새로운 지평을 열고 있습니다.

마지막에 쓰기

이 기사는 주로 현재 뜨거운 주제에 초점을 맞추고 참조용으로 세 가지 주요 메모리 회사의 생각을 공유합니다.

Techinsights에 따르면 앞으로 DRAM은 DDR5, LPDDR5/5X, GDDR6/6X, HBM2E/HBM3/HBM3E 및 LLDRAM(Low Latency DRAM)과 같은 애플리케이션에 여전히 중요할 것입니다. 인메모리 처리(PIM) 및 컴퓨트 익스프레스 링크 니어 메모리 처리(CXL-PNM)와 같은 혁신으로 성능과 효율성이 향상되고 있습니다.

테크인사이트는 삼성전자와 SK하이닉스가 DDR5, LPDDR4X, LPDDR5, LPDDR5X 등 D1a, D1b 셀 설계 제품을 최소형 12나노급 D램 셀 설계로 상용화했다고 밝혔다. 두 회사 모두 EUV 리소그래피 도입을 주도하고 있으며, 마이크론은 1α 및 1β 세대에 ArF 및 ArFi 기반 패터닝을 계속 적용하고 있으며, 1γ 세대에 EUV를 도입할 계획입니다. 삼성전자는 EUV 리소그래피를 D1a, D1b 세대에서 5개 이상의 마스크로 확대한다. SK하이닉스는 유사한 EUVL 전략에 따라 D1a, D1b 세대에 이를 적용해 왔으며, 향후 세대에는 EUVL 단계를 추가할 계획이다.

"내년 초 주요 공급업체는 D1c D램을 양산에 출시하고, 2026년 또는 2027년에 최종 10나노급 D램 장치(D1d 또는 D1δ 노드)를 출시할 예정입니다. 2030년까지 DRAM 기술은 0a, 0b, 0c 또는 0α, 0β 및 0γ 세대를 포함한 한 자릿수 나노노드로 축소될 것으로 예상됩니다. 삼성전자는 VS-CAT과 VCT 3D D램을, SK하이닉스와 마이크론은 수직적층 D램을 개발 중이다. Techinsights는 강조했습니다.

Techinsights는 DRAM 기술의 미래가 고성능 애플리케이션 및 신흥 기술에 대한 증가하는 수요를 충족할 수 있을 것이라고 믿습니다

'Semiconductor' 카테고리의 다른 글

| 반도체 제조 공정 - Etch Technology (5) | 2024.07.17 |

|---|---|

| CPU 생산 공정 - 기본 다이어그램 (1) | 2024.07.17 |

| HBM 새로운 경쟁 개시 !!! (0) | 2024.07.17 |

| 삼성 전자 - 평택 P4공장 낸드설비 발주 재개 (0) | 2024.07.17 |

| 24년 - 반도체 업체 실적 - 45곳 - 중국 (0) | 2024.07.17 |

댓글